I don't trust your word for it because you're not citing any actual numbers or public statements from TSMC, their customers, or anyone familiar with the actual performance of the node. Furthermore, what you're saying directly contradicts any credible sources that I've come across. Let's start with Anandtech's own synopsis:

https://www.anandtech.com/show/16639/tsmc-update-2nm-in-development-3nm-4nm-on-track-for-2022

The only rational takeaway from that report is that when TSMC N3 reaches HVM, it will be the most advanced manufacturing process available, offering the highest transistor density, highest performance, and lowest power of any node past or present. Unless you expect the finished wafer cost to rise more than 70% over N5, then N3 will also offer the lowest transistor cost. In fact, it will almost certainly provide the lowest transistor cost in history. Are these gains less than what we might have expected historically? Absolutely—Moore's Law is running head first into the hard reality of physics.

Even if you go by the wafer costs from the CSET paper,

which are almost certainly high of the mark, the increase in wafer price for N5 still did not exceed the increase in transistor density over N7. Transistor prices still went down even if they didn't decrease as much as Moore's Law would have predicted. Even as the rate of progress slows down, you're still making progress.

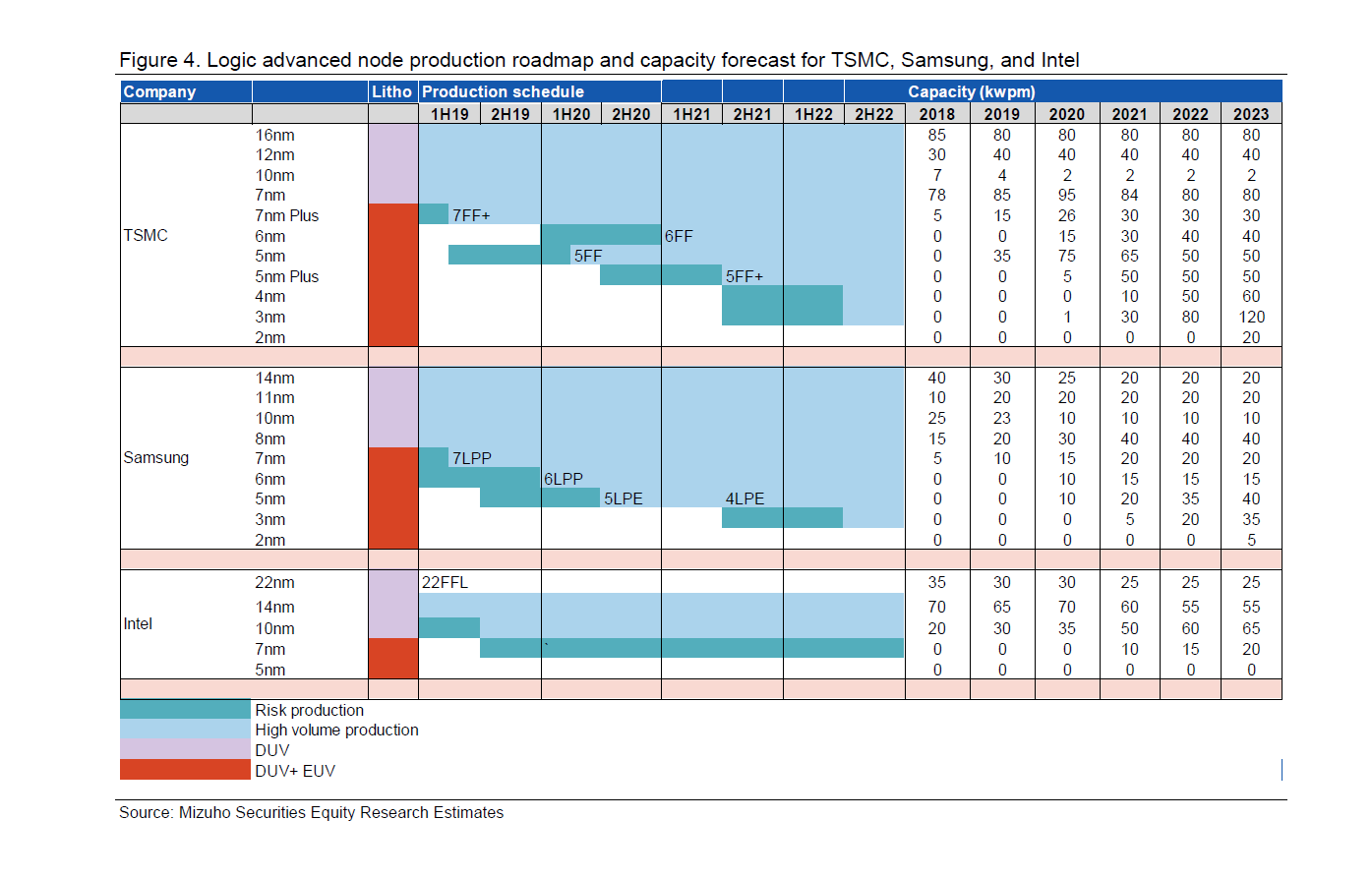

As for cycle times, I haven't seen anything that gives me a solid compare between nodes. The basic rule of thumb is that even though EUV steps take longer than DUV, every time you can replace a multi-patterned DUV layer with a single EUV layer, you reduce the number of steps and masks, which in turn reduces both cycle times and cost. Every time you have to add additional multi-patterning steps, you increase the number of masks, cycle times, and cost. I think N3 increases both the number of EUV layers and use of multi-patterning over N5, so we should expect longer cycle times. There's no way TSMC's wafer price will increase by 70% over N5 though, and they stuck with FinFET for N3 which should help yields and keep design costs somewhat in check.