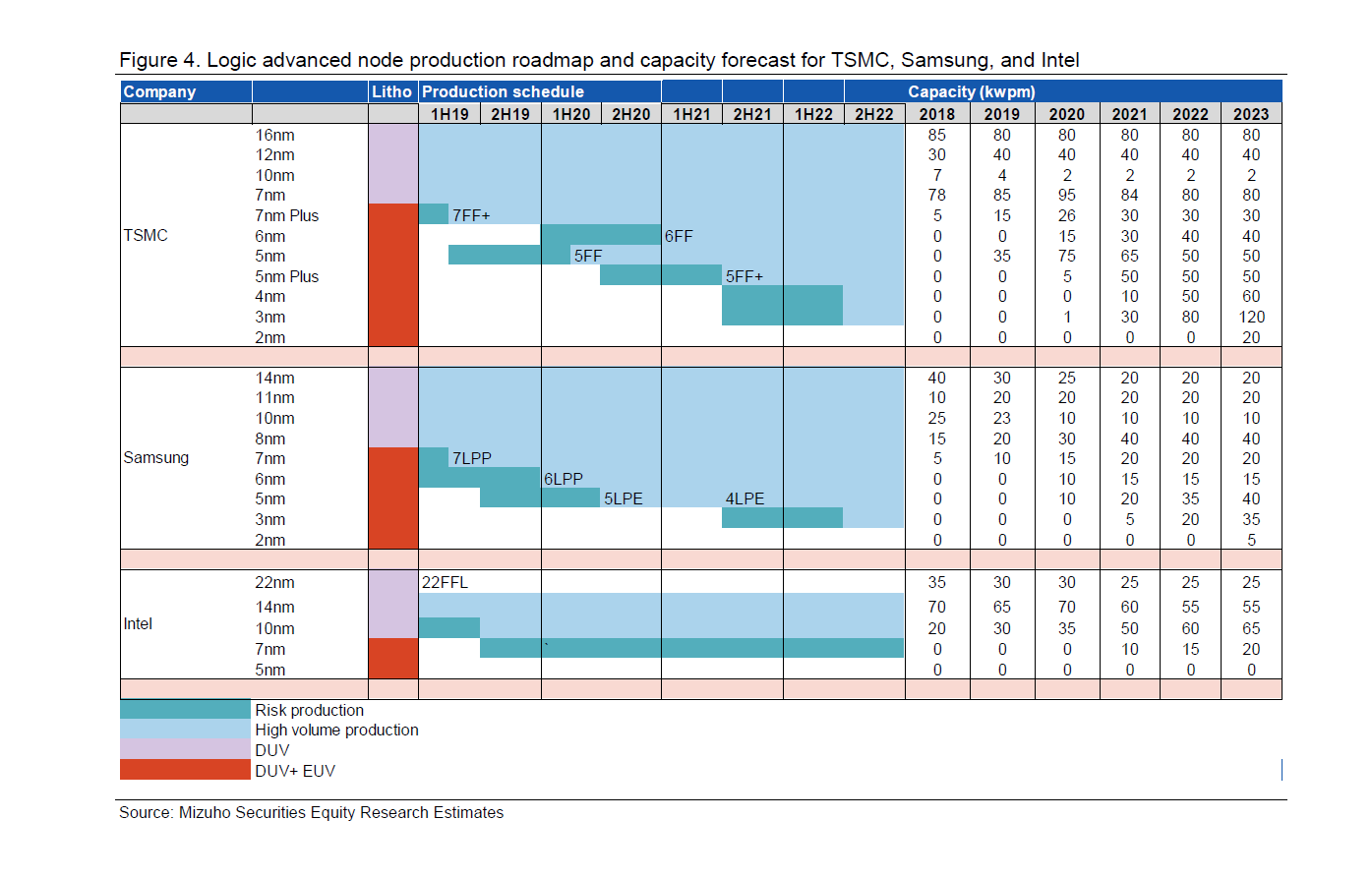

Everyone has trouble getting EUV equipment. Unlike Intel who doesn't know how to use it, TSMC and Samsung are not getting enough EUVs. According to ASML, each 45k wpm requires 10~20 EUV scanner for 7~5nm nodes(3nm will need more), but ASML makes ~30 EUV scanners every year(Plans to boost to 60 by 2023 but not here yet).

So each year, ASLM can supply 100k wpm EUV fabs worldwide. The world lacks 15 EUV scanners in 2022 according to the source. Since Samsung bought more EUV than TSMC in 1st half of 2021, we can't say that TSMC got sufficient EUV by buying every EUV possible.

And now, DRAM makers are starting to purchase EUVs(2~10(?!) EUVs per 100kwpm) . In DUV days, TSMC alone had 100k~120k wpm for each leading-edge nodes. But now, that 100k will be separated to TSMC, Samsung and later, Intel.

These are ordered years in advance, so a difference like Samsung getting more than TSMC in the first half of this year doesn't say anything about whether TSMC got a "sufficient" number of EUV machines for their needs. It isn't like Samsung got up early on January 1st and placed put in a bunch of orders and too bad for TSMC who overslept. Foundries are probably taking delivery on orders they placed in 2018 or even earlier.

Since the orders are placed well in advance, but they don't have confirmed delivery dates until a lot sooner, foundries probably can't accurately plan number of wafer starts or possibly even node availability until they get those confirmed delivery dates from ASML. ASML doesn't so much have production targets, as production goals. If they can find a way to produce two or three more scanners than they had planned for that year, they will do so and foundries will be happy to take delivery a bit earlier than they had been told a year before when delivery dates were confirmed.

Supposedly when Intel had all their problems (before they replaced their CEO) they canceled orders from ASML. That's what led to speculation from some that Intel would no longer pursue advanced nodes and would go fabless in the long run. Given this was right around the time they made the deal for leading edge TSMC capacity my bet has always been that they traded those orders (i.e. "spots in line for delivery") to TSMC in exchange for being able to buy the capacity those scanners made possible for TSMC to add. TSMC has said they will be doing 30k N3 wpm in risk production and 105k wpm in full N3 production - about double N5's full production number. So Intel may get a lot of N3 slots, depending on how much of that wpm difference is accounted for by machines that Intel had ordered that TSMC is apparently getting instead.