NostaSeronx

Diamond Member

- Sep 18, 2011

- 3,811

- 1,290

- 136

Fusechip & semiwikiOne of these days you will give a source or drop a link.

Most of the stuff added to 5LPE was already in TSMC's N7P. The only thing it lacked was EUV and the enhanced routing efficiency/yield that it provides.

N7+ is a big shrug as most companies who wanted to go on it have dropped it for N6 instead. Technically, more room for AMD, but N7+ and N6 use the same Fab. With N6 to ramp to a higher volume than N7+.

Also, N6 might have + option to support RTOs from N7+ w/ 4 layers to N6(+?) w/ 5 layers and NTOs from 7+ to support even further optimization of the 5-track 7+ option. N6 is suppose to evolve from N5 learning, so it going to N7+ or further than it, is a given.

Also, note there is no discrete N6/6nm node on the website: https://www.tsmc.com/english/dedicatedFoundry/technology/logic.htm

Instead, it is in the N7/7nm section => https://www.tsmc.com/english/dedicatedFoundry/technology/logic.htm#l_7nm_technology

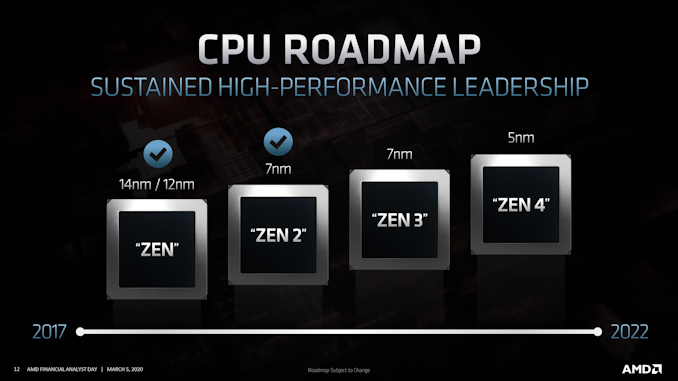

It is completely feasible that "7nm/N7" mentioned can refer to any node in the family; N7, N7P, N7+, N6

Last edited: