It is not a ring, it is a bridge, but since you said that Intel solution is suboptimal, what would be the optimal solution for you? and how AMD solution is better than Intel suboptimal solution?

Yes, it's a ring. It looks like a ring and it works like a ring. You can call it whatever you want though, it's your choice. It's suboptimal because it's got too many hops. It works best with slightly less cores, 24 cores are stretching the concept.

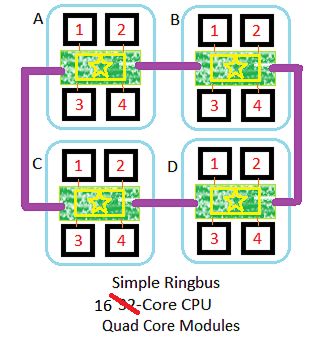

I'm not saying AMD's solution is better, I'm only saying the whole GMI+SDP architecture was designed from the ground up to support 4 dies and a total of 32 cores. While the ring architecture that Intel uses wasn't designed for 32 cores at all, not even for 24 cores.

To make Intel's ring architecture better, you would need to lessen the number of hops it takes to reach cores. You could for example connect each core to not only their neighboring 2 cores, but 2 more cores from the other side of the ring for example. A 2D mesh and especially a 3D mesh would be even better. AMD's solution is completely different, since it has 4 cores in a core complex, 2 core complexes on a die, and then dies are connected to each other inside the CPU package. But those dies are connected quite well (IMHO AMD did a great job on that), so what we'll need to see is what the worst latency would turn out to be.