AMD Polaris

Junior Member

Or the 8C/16T Intel parts. Or the 10C/20T Intel parts.

Price wise I wouldn't be that sure...

Or the 8C/16T Intel parts. Or the 10C/20T Intel parts.

Interesting, I remember reading rumors that there wouldn't be 4 core variant initially and only 6/8.Zen ES is at the moment in revision A0 - it might not be a suprise.

Core counts are: 4c/8t, 8c/16t, 16c/32t, 32c/64t. As it seems now there won't be a 6c/12t at the launch

4 variants of ES Zen are available at the moment:

AM4 8 cores with 95W TDP

AM4 4 cores with 65W TDP

SP3 24 cores with 150W TDP

SP3 32 cores with 180W TDP

The most exciting part is core clock. The 8c/95W variant's base clock is 2.8GHz, all core boost is 3.05GHz and maximum boost is 3.2GHz.

The 4c/65W part's clock is the same. (I would expect 3.5GHz base clock for a retail 4c/95W variant.)

To me it sounds like some wishful thinking written from some AMD fanboy. And given how many fakes we got from AMD stuff in latest years I somehow doubt this is true. It's not even clear if these predictions are based on some official data/tested data or just some stuff made up from your wishful thinking. That's very dangerous. I think this is mixed with wishful thinking.

One thing I can tell you for sure: what he said is not fake, at all.

Wishful thinking would have been a 4c/8t Summit Ridge already running at over 4 GHz clocks in a flawless AM4 motherboard and executing a bunch of benchmark software with zero issues.

AFAIK Intel has no answer for the 32c/64t Zen variant, so it could be a great win for AMD on the server market.

Price wise I wouldn't be that sure...

Why should we trust you? Another low posting user coming from nowhere, everyone could post the same.

Do you know that 32 cores without FMA/AVX on the server market is the old AMD failed strategy of providing more cores to reach the same performance level, do you?

And it doesn't work, because the moment you add more cores you add up to leakage and you end up with worse performance/watt.

Do you know that 32 cores without FMA/AVX on the server market is the old AMD failed strategy of providing more cores to reach the same performance level, do you?

Do you know that 32 cores without FMA/AVX on the server market is the old AMD failed strategy of providing more cores to reach the same performance level, do you? And it doesn't work, because the moment you add more cores you add up to leakage and you end up with worse performance/watt.

Are you saying that Intel wouldn't be able to roll out a 32-core BDW-EP with a cca. 2 GHz clock rate? Why would that be impossible to do? And keep in mind that a Zeppelin (Zen) core is simpler (leaner) than a BDW core, so piling them up might be a bit easier.

Depends on whether you have a workload that cares about vector FP throughput. Plenty of workloads focus on integer throughput.

And if you have a workload that scales well the 8-wide FP vectors over 32 cores, you should probably be looking at putting it on a GPU anyway.

Isn't hose the features that will be remedy with ZEN+ when it comes year or two later?

Think harder, Intel had this choice and instead took the other route. Why?

A 24-core server part wouldn't make a huge buzz, we've already seen that with BDW-EX. But making both a 24-core and 32-core server CPU could work out as a breaking news and help AMD to capture the attention of server folks.

so, I don't think a 32-core BDW-EP/EX could work well with their current 2-ring architecture. It would most likely require a more complex solution to scale well. While AMD chose a different path and that one could work well with up to 32 cores. Otherwise, if that would be hugely inferior to a 24-core layout, AMD simply wouldn't bother making a 32-core part...

Usually in the server market it doesn't matter how much buzz you make, it's more about delivering the promised performance within the efficiency targets, something that Intel has been doing in the last 10 years.

Would you care to explain how Intel dual ring solution for 32 cores would be worse than the MCM solution AMD is going to field with Zen? Unless AMD discovered a magical pixie dust that will magically solve the problem, AMD solution will be even worse than Intel's.

Would you care to explain how Intel dual ring solution for 32 cores would be worse than the MCM solution AMD is going to field with Zen? Unless AMD discovered a magical pixie dust that will magically solve the problem, AMD solution will be even worse than Intel's.

AMD Polaris said:AM4 8 cores with 95W TDP

AM4 4 cores with 65W TDP

The most exciting part is core clock. The 8c/95W variant's base clock is 2.8GHz, all core boost is 3.05GHz and maximum boost is 3.2GHz.

The 4c/65W part's clock is the same.

GMI and SDF will do the magic. I'm sure you know what they stand for and how they work 😉

As for 32 cores in BDW-EP/EX: there are certain hops that you can quite easily pile up and make things worse. The data packets have to travel around in those 2 rings, and the size of the rings (the number of hops) is quite an important factor. Yes, you could add 4 more cores per each ring, but I'm sure in many workloads it would make things worse, even at similar core clocks than with the current top-of-the-line 24-core BDW-EX... AMD's solution doesn't use any rings BTW.

It doesn't matter whether the workload can scale over 32 cores with decent throughput, but whether the workload can be processed in an efficient manner. This is a glass-jaw in AMD architecture, a trade-off they are making. Whether they are making this due to 1)lack of resources, due to 2)being delusional or 3)disruptive business strategy is open to question, but given that Intel has much better access to the server market customers than AMD can dream of, I wouldn't put my bets on 3), I would go for 1) but wouldn't discard 2).

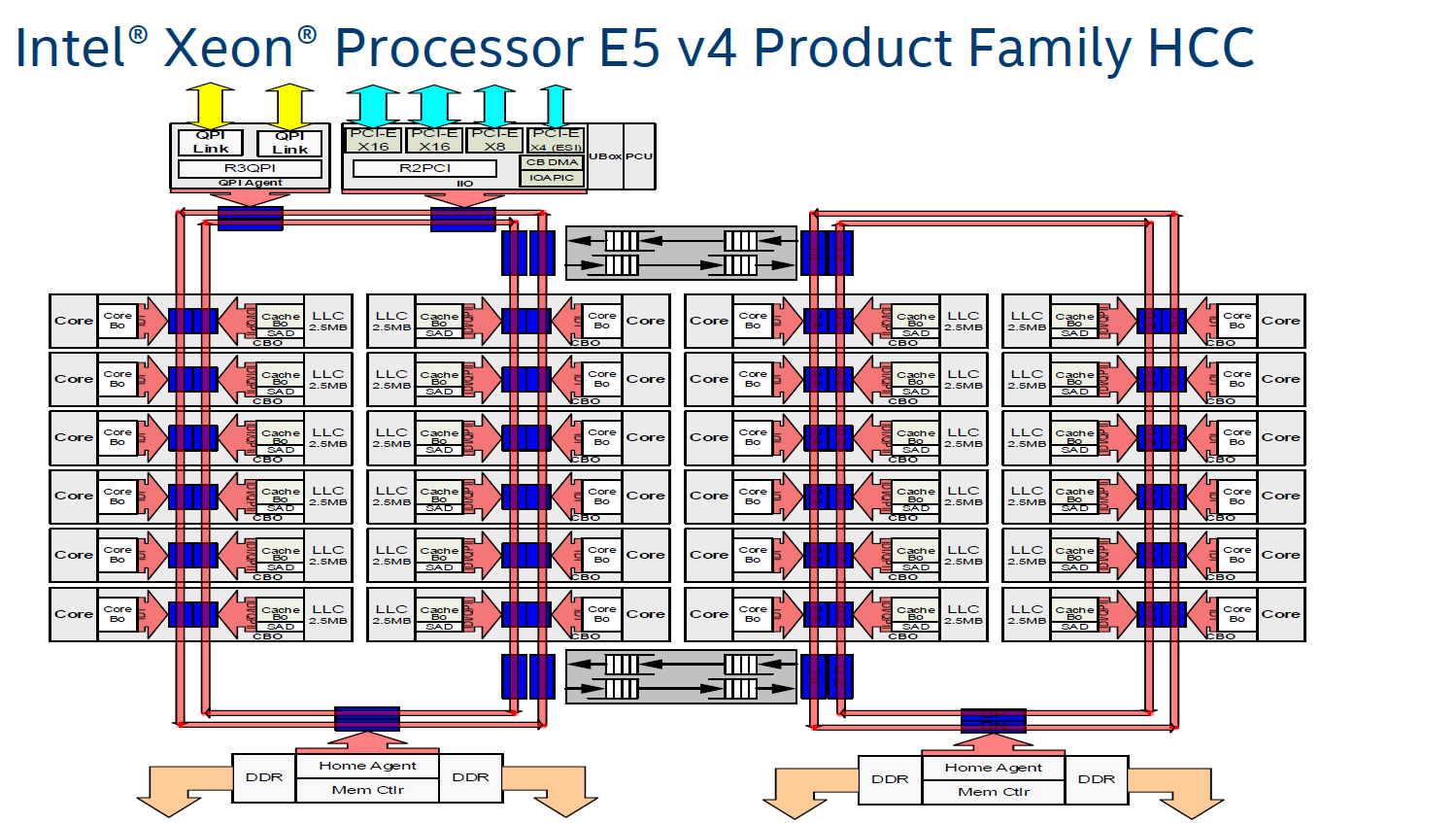

I'm not sure you are familiar with the current Xeon layout. They have four blocks of 6 cores each, each pair of blocks is connected by two rings and there is a bridge between the two rings of each pair, so you don't add four cores to each ring to reach 32 cores, you add two, and FYI the top Skylake-EP, the one that will compete with Zen, will have 28 cores.

My one and only guess was 2.5 3.2 🙂If those clocks stated by AMD Polaris are even remotely true, I cannot say I'm too surprised. They align perfectly with the latest of my estimations I made in post #1259 (2600MHz (±200MHz) base and 3200MHz (±200MHz) maximum boost).

As explained in post #2044 I assumed that AMD used 2:1 scale in their famous "Orochi vs. Summit" and "Excavator vs. Zen" charts.

Also if the chart was infact about Cinebench R15 (which is highly likely), then the "Orochi" CPU they used in the comparison is likely to be the FX-8350 / FX-8370 (and not the -E model I previously speculated.) These two CPUs have the same base clock and TDP, meaning they will perform identically in multithreaded workloads. The FX-8350 / FX-8370 scores 643 points in Cinebench R15 MT. Multiply that by 1.5x and you'll end up with 965 points. Based on the expected IPC improvement and the clock estimation, Zeppelin should match this target at the 3050MHz "all core boost" if the SMT yield is ~11.7%. A pretty plausible SMT yield for a first implementation, IMO.

I ran the claimed figures through (with the expectation that the IPC is exactly 40% over Excavator).

Used Cinebench R15 only, since it is properly threaded workload which doesn't use modern instructions.

If the sustained base clock during CB R15 MT is 2.8GHz, 8C/16T Zeppelin should score: 833 / 872 / 912 / 952 / 991 (5 - 25% SMT yield)

If the sustained base clock during CB R15 MT is 3.05GHz, 8C/16T Zeppelin should score: 907 / 950 / 994 / 1037 / 1080 (5 - 25% SMT yield)

The single threaded score should be around 113 points at 3.2GHz.

Meanwhile Intel 8/16C parts would score as follows, at the same clocks:

Sandy Bridge-E = 971 / 1058 (2.8GHz / 3.05GHz)

Ivy Bridge-EP = 1002 / 1091 (2.8GHz / 3.05GHz)

Haswell-E = 1091 / 1189 (2.8GHz / 3.05GHz)

Broadwell-E = 1117 / 1217 (2.8GHz / 3.05GHz)

Intel ST at 3.2GHz:

Sandy Bridge = 114

Ivy Bridge = 117

Haswell = 128

Broadwell = 136

Skylake = 139

Based on these figures 8C/16T Zeppelin clocked to 2.8GHz / 3.05GHz would compete in multithreaded performance with i7-6700K (except in AVX2, most likely).

I'm familiar, but the 2 rings I've mentioned are still just two 2-way rings, and 12 cores are connected to each other by a double ring:

The question about the speculated Clocks from Mr. Polaris, the real question is, do early Engineering Samples clock near final product clocks?

😀