I don't think so. There is no OEM profit margin. Microsoft does not sell to OEMs for further mark up. Microsoft sells directly, likely at cost or below at first. Later in the life cycle, the costs come down somewhat.

If new XBOX sells for $600, your cost estimates are off by factor of 2x-3x.

A quote from Star Wars "You are greatly mistaken about a great many things".

The fact will be that a game console processor will need to be considerably lower cost than a desktop processor. No one would tolerate a 2K console.

No one is using 75mm² of N2P silicon for CPUs just to run games at 30/60 FPS.

Agree. I wouldn't be surprised if the XBox processor is customized for the gaming console though.

The CPU would be likely single N4P Zen5 die and the GPU can use N3C with advanced packing would be lot cheaper for AMD to cook and should be cheaper to produce.

Possibly so. The idea is right on track. AMD will be looking to minimize cost on this one.

AMD has been pioneering in this area, and, until now, did not have a very effective and affordable 2.5D solution.

Now, AMD has it in InFO, and is expanding its use.

Is it illogical to expect that AMD will expand it further?

To stop Arm encroachment into datacenter, to change value proposition for Hyperscalers so that they buy more AMD product and spend less on designing their own.

Even Broadcom is beating AMD in semicustom, which is sad.

It's a good question (chiplets vs monolithic). I think it will depend on which approach is less expensive.

As for the Arm encroachment into DC, it doesn't seem to be having much effect on AMD's rapidly increasing margin and volume in DC.

Remember to take your salts and everything

Do we have any confirmation that its the Zen4 team thats responsible for Zen6 ?

My take, Zen6 will win everything thats not

embarrassing parallel and Nova Lake will comsume 350-400w when tuned to actually have decent cinebench performance

Very few apps/games/benchmarks can take full advantage of the 48 threads/cores is also a drawback, espescally if the rumored 8P16E + 8P16E + 4LPE(SOC) on two different compute dies are true, making the windows scheduling doomed to fail

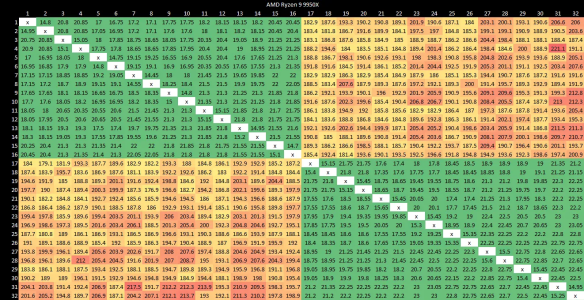

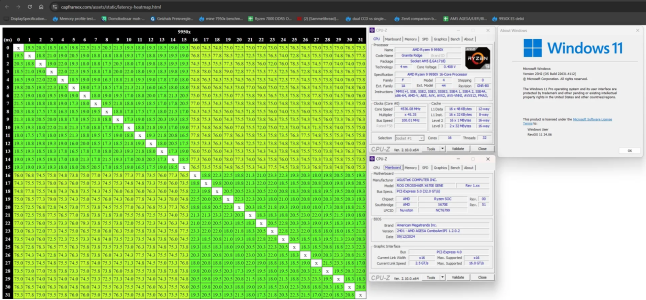

Possibly so; however, I still have hope for NVL as I believe those P cores on ARL are being seriously hampered by latency .... that may get cleaned up in NVL providing a Zen 2 to Zen 3 moment for NVL.

AMD hasn't hit a frequency target in like 5 years so Zen6 perf is still very TBD.

Well, MLID seems to think AMD is looking at a 6.5Ghz boost clock

😉. Seriously, how can we doubt such a thing?

I have to admit that the rumor did spike my interest. I have simply given up on clock speed increases over the last decade. If this is even partially true, a 6Ghz Zen 6 would be very potent indeed.

With AMD launching Threadripper 9xxx parts next month, how many people are seriously going to wait for a 400w Nova Lake-S? That part will probably be vaporware and will lose to 64c Threadripper, not to speak of the 96c PRO part.

It is my opinion that anyone that NEEDS that many cores will also NEED the additional bandwidth provided by Threadripper. I also believe that the same people are doing professional work and will easily shell out the $$$ for this kind of performance.

Even AMD has a story that the next Zen6 laptop CPU will have a smaller LP core than the Zen "C" core.

Every AMD is installed in many models from the Zen5 laptop CPU to the Zen C. The weak Windows scheduling is a bad thing for AMD as well...

I think you are partially correct. I don't think that AMD intends to create a LP core that is architecturally different from Zen 6. I think it will go as follows:

Zen 6 full - base

Zen 6c - base minus lots of L3

Zen 6LP - base minus lots of L3 and designed with transistors that are specially designed to operate at lower power at the expense of higher clock speeds.... they might actually be larger than Zen 6c.

day 9592 of anandtech posters pretending there's a mythical workload that scales infinitely with cores, while not giving a crap about membw AND not needing to be correct (aka requiring ECC from workstation/HEDT boards).

I agree. Anyone that needs 48 cores also happens to be the kind of persona using the kind of application that needs lots of memory bandwidth and the persona has tons of $$$ they are willing to pay for that performance.

Will desktop Zen 6's IO die be reworked or it will continue to gulp 20-40W doing nothing?

I think that Zen 6's IOD is going to be a huge improvement over Zen 5's and will likely be the star of the show (so to speak).

Why not disable it and save the extra silicon validation time?

Answer: Because their SMT is actually better than Intel's excuse of hyperthreading, so much that they disabled it in Arrow Lake because they were afraid of the ST performance going even further down.

Intel really didn't need to rush Arrow Lake. Imagine if they had worked just a bit harder to enable HT (even their half assed attempt), we could've had the first x86 consumer CPU with 48 threads in 2025!

It is true that Intel's SMT was much less value than AMD's. I think it came down to Intel betting on ST performance enhancements in ARL and they needed the die space for that more than they needed SMT. The problem I see with this strategy is that in DC, the PPA of SMT (at least for AMD) is very valuable!

I get the feeling that they'll be selling them in 12, 16, 20, and 24 core varieties for quite a premium for a while.

I totally agree with this.