Covfefe

Member

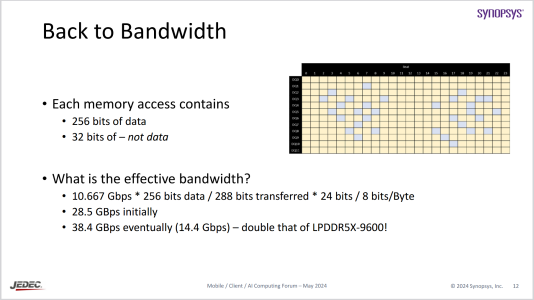

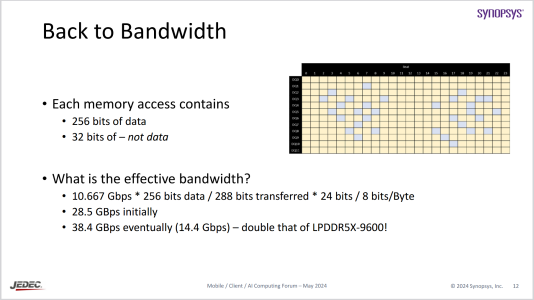

According to JEDEC, LPDDR6-14400 has 2x the bandwidth of LPDDR5X-9600. https://www.jedec.org/sites/default/files/Brett Murdock_FINAL_Mobile_2024.pdf

Extrapolating from that. A 192-bit LPDDR6 memory bus has 1.33x the bandwidth of a 128-bit LPDDR5/X memory bus of the same per-pin speed.

A LPDDR6-10667 192-bit config (which should be the base LPDDR6 config for laptops) has 89% as much bandwidth as Strix Halo.

Extrapolating from that. A 192-bit LPDDR6 memory bus has 1.33x the bandwidth of a 128-bit LPDDR5/X memory bus of the same per-pin speed.

A LPDDR6-10667 192-bit config (which should be the base LPDDR6 config for laptops) has 89% as much bandwidth as Strix Halo.