PS, about...

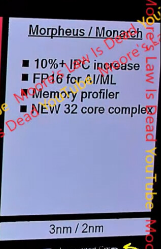

...the actual IPC increase we'll see for desktop...

First, the figure is for SPECrate 2017 Integer

¹ — that's different from, say, Cinebench R23 which is scalar FP

² with light use of the memory subsystem, and even more different from average frames per seconds in video games. :

-)

Second, it is for absolute computer performance at unknown core clock frequencies. What we more or less know is that it's 2x Turin-dense top SKU (3nm, 192 cores/socket, 500 W/socket) versus 2x Venice-dense top SKU (2nm, 256 cores/socket, 600 W/socket). Many have tried to derive "IPC" uplift from such whole-computer performance uplift figures before, but as we know all too well, there really is quite a bit of guesswork involved in such attempts.

________

¹) SPECrate 2017 Integer actually

does have three game subtests in it: Chess, Go, and Sudoku. :

-) Of course SPEC does not call them g4m1ng subtests, but, and I am not kidding, AI subtests. Furthermore there are Perl interpreter, C compiler, route planning, LAN/WAN simulator, XSLT converter, x264 video compressor, and xz data compressor subtests.

edit:

²) or

more correctly, "a mix of scalar SSE and 256-bit AVX".