- Mar 3, 2017

- 1,779

- 6,798

- 136

Apropos practical reality. You must have missed at least two thirds of my post, if not more. I direct your attention to just the topmost of the several parts of my post:

Even if we restrict ourselves to a PC with the power and performance level of the 7945HX (and which GPU?), your portable computer is a *lot* louder than a decently built stationary computer. Furthermore, keyboard and screen of your portable computer are bolted onto each other and are therefore by definition not ergonomic. Unhealthy in prolonged use.

oh come on bro

ergonomics: laptop wins period. use it as-is or with peripherals monitors keybmouse etc. no questions

No way this is N2P/x those are entering HVM in 2026 this means products in 2027 N3P may be possible cause N3E and N3P is forward compatibleIt's not N3e.

Either N3p or N2p/x, depending on the timeline.

This is the ergonomics forum, are you the guy with the keyboard? Go sit next to the lady with the mouse please, we'll send the boy with the alarm clock when we need you.Am in the wrong thread 🤔

Yes I am the guy with a broken keyboard I am here for a RMAThis is the ergonomics forum, are you the guy with the keyboard? Go sit next to the lady with the mouse please, we'll send the boy with the alarm clock when we need you.

Absolutely nobody have said anything about scaling Andoid Apps to Windows.No.

The ISA games are compiled into is mostly a non factor. You write in C or whatever and compile it, and it doesn't matter much whether it compiles into x86 or ARM. You might call some libraries or even write a few short assembler sections in tight loops to insure the best SIMD code can be used, that's about it.

The difficulty in writing and porting games is in everything that surrounds that code you write - the OS and GPU drivers. Having competitive ARM SoCs does nothing to help Android games run on Windows.

Wont be N2 unless its still 3 years out. N3P is possible, but so is N3E. Either way, max frequencies arent going up, and it will bring a ~10% IPC uplift. Most important changes will be in idle power consumption, 12 or 16 core CCX for consumer, memory controller/subsystem/interconnect, iGPU.It's not N3e.

Either N3p or N2p/x, depending on the timeline.

[citation needed]Wont be N2 unless its still 3 years out. N3P is possible, but so is N3E. Either way, max frequencies arent going up

Cited by broken Keyboard owner[citation needed]

Im talking about consumer Zen 6. It will not use N2. Enterprise will use 2nm for dense just like Zen 5 did. We have the roadmap, it was 100% accurate for Zen 5. The only possible thing that could change is if 2nm gets delayed. Zen 6 +10% IPC. Only mysteries will be what they choose to do with X3D this go round. Mark it.[citation needed]

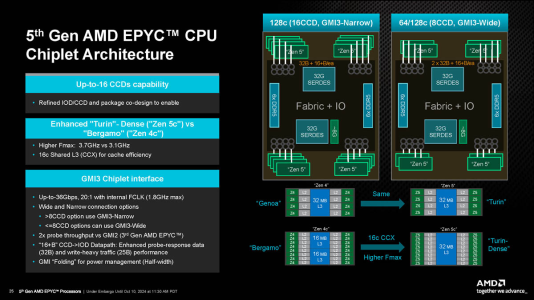

I'm aware of the slide. It does not say anything about clock speeds.Im talking about consumer Zen 6. It will not use N2. Enterprise will use 2nm for dense just like Zen 5 did. We have the roadmap, it was 100% accurate for Zen 5. The only possible thing that could change is if 2nm gets delayed. Zen 6 +10% IPC. Only mysteries will be what they choose to do with X3D this go round. Mark it.

Its correct. Depending on what its referring to, which is not entirely clear, there's low power cores in Strix Halo (this is probably what its referring to), low power 5c cores in Strix and Krackan Point, and low power Zen 5c 3nm cores in EPYC.I'm aware of the slide. It does not say anything about clock speeds.

The slide is also not entirely correct wrt/ Zen 5. There is no low power option (yet at least).

No? The official term for 5c is "Dense". You don't need to go further than the Zen 4 roadmap item to verify that.Its correct. Depending on what its referring to, which is not entirely clear, there's low power cores in Strix Halo (this is probably what its referring to), low power 5c cores in Strix and Krackan Point, and low power Zen 5c 3nm cores in EPYC.

there's low power cores in Strix Halo (this is probably what its referring to)No? The official term for 5c is "Dense". You don't need to go further than the Zen 4 roadmap item to verify that.

View attachment 115117

So the CCDs that are featured to a first order in the desktop part, they have an actual PHY that connects the two dies. And so there is there's actually a distance that it needs to travel. It's a SERDES and you're able to go some distance between the two. That's how we've always connected the two. And that's a low cost interface, if you will. It is a high bandwidth interface. But that had low power states that could only take it so far. And you had retraining and latency implications every time the chip went down and came back up and so on. So for an always on kind of a desktop kind of machine, that seemed like the best interconnect to connect that as we try to build this into an APU. The first thing we had to do was to change the interconnect between the two dies. And so the CCD that you see here, the core die that you see here, has a different item. That's the first change.

That's a sea of wires. We use fan out, we're for level fan out in order to connect the two dies. So you get the lower latency, the lower power, it's stateless. So we're able to just connect the data fabric through that connect interface into the CCD. So the first big change between a Granite or a 9950X3D and this the Strix Halo always the die to die interconnect. Low power, same high bandwidth, 32 bytes per cycle in both directions, lower latency. So everything that and almost instant on and off stateless because it's just a sea of wires going across. So it's a little [bit of a tradeoff] of course, the fabrication technology is more expensive than the one over there [points to a 9950X3D], but it meets the needs of the customer and the fact that it has to be a low power that can actually connect.

We don't have any official confirmation for that. Mahesh Subramony also gave no indication that those ever existed.there's low power cores in Strix Halo (this is probably what its referring to)

Read above. The CCDs and cores in Halo are different from desktop and enterprise. They are purpose built for low power. The roadmap is correct.We don't have any official confirmation for that. Mahesh Subramony also gave no indication that those ever existed.

Read above. The CCDs and cores in Halo are different from desktop and enterprise. They are purpose built for low power. The roadmap is correct.

And so the CCD that you see here, the core die that you see here, has a different item. That's the first change

www.notebookcheck.net

www.notebookcheck.net

You're quoting a typo in the transcript, what he actually said is the following:Yes it does. Do you think they built a completely different CCD if they didnt need to?

And so the CCD that you see here, the core die that you see here, has a different die to die interface. That's the first change.

These have the 512 bit data path. It is a full desktop architecture. We have binned the parts for efficiency. So it might not hit the peak frequency that you would see on the desktop. That's one of the second differences in the cores you would find over here and the cores over there.

So these are binned, the same architecture, the same set of pipes, the data parts are the same. The differences are in how we bin the part and how we connect the two dies.

You're quoting a typo in the transcript, what he actually said is the following:

Timestamp from the video:

Later he goes into more details:

Die to die connection changes require a new die. This is done for low power, who here is disputing that? Its a new low power core option. You want low power cores, you need that different CCD and die to die connection. Its not mentioned, but probable, that the die to IOD connections differ as well, designed for power savings.Even without the typo it was clear by the surrounding context they were talking about the d2d connection, but it’s good that the correct transcript says it outright.

No, they do not. They just require that the CCD features both interfaces. Same as MI300A, same as X3D, they all use the same CCDs as the vanilla products.Die to die connection changes require a new die.

No. GMI is uncore.Its a new low power core option.

Per-core power is "low" in several Turin SKUs as well.I still maintain that the roadmap is referring to the Strix Halo cores, as they are not C cores, yet can operate at much lower power than standard cores.