- Mar 3, 2017

- 1,779

- 6,798

- 136

Will the chipset actually make a difference for memory speeds? I've heard both, but I thought the CPU memory controller was the limitation.

230w PPT oc idle 100w?! And core temp only 23c? That’s definitely a sub ambient temperature cooling.That's the sad state of tech journalism today... Everything is sensationalized and WTFtech led the way in the 2010s.

That explains the really good temps, then. There's a bunch of people on Xitter who are reacting to the WTFtech/Videocardz articles about the info you shared, but those articles don't do a good job of clarifying why the temps are so good. It's leading people to incorrectly believe that Zen 5 is super easy to cool and/or super power efficient.

For example, from the Videocardz article, just no mention of cooling method whatsoever.

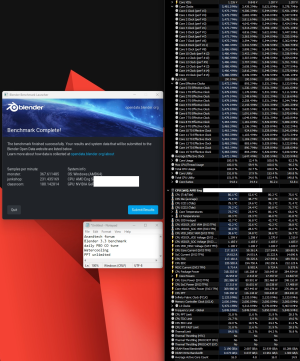

View attachment 102915

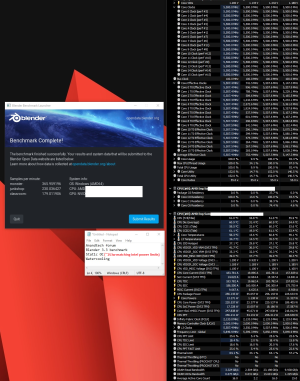

Same with WTFtech:

View attachment 102916

So often authors just steal whatever info is eye-catching for their article but fail to represent the source faithfully because they don't bother reading the rest of the thread... SMDH.

View attachment 102918

Unbelievable is right.

Custom loop is not bounds and leaps better than typical AIO at keeping temperatures low for such a short benchmark, so it'd be the same with any other cooling solution (provided its coldplate is not U shaped like most Intel-optimized setups are). Also, you don't have to buy expensive german parts, I make do with full 100% chinese setup (a knockoff mora, some cheap threadripper-adapted waterblock with a finned coldplate that covers whole CPU etc), and it wouldn't be that much worse as compared to legit MORA/ XSPC Raystorm etc.Dissapointing climax.

If you tweak powerplan a bit and there is browser open in the background, idle cpu power consumption is around 60W for me personally (20W of which is SoC)230w PPT oc idle 100w?!

Next we will hear that the "daily OC/PBO+ CO tunning" is -30CO max fclk with high vsoc/vddg and mem oc+tertiary timings tuned.Custom loop is not bounds and leaps better than typical AIO at keeping temperatures low for such a short benchmark, so it'd be the same with any other cooling solution (provided its coldplate is not U shaped like most Intel-optimized setups are). Also, you don't have to buy expensive german parts, I make do with full 100% chinese setup (a knockoff mora, some cheap threadripper-adapted waterblock with a finned coldplate that covers whole CPU etc), and it wouldn't be that much worse as compared to legit MORA/ XSPC Raystorm etc.

It's higher than my increased voltages and tuned tertiary 6400/2133fclk setup on the 7950X, so he's done something really bad.Next we will hear that the "daily OC/PBO+ CO tunning" is -30CO max fclk with high vsoc/vddg and mem oc+tertiary timings tuned.

The high W on the soc was suspicious.

You guys know both soc voltage and soc powerusage is showing in the screenshots ?It's higher than my increased voltages and tuned tertiary 6400/2133fclk setup on the 7950X, so he's done something really bad.

There's no reason the IOD would be ES quality silicon since it's reused from Raphael. His VSOC looks decent. I imagine it's other voltages HWINFO isn't showing he has cranked.You guys know both soc voltage and soc powerusage is showing in the screenshots ?

ES is ES for a reason i guess

Given they just doubled FP/SIMD throughput for Zen2 they wouldn't have done hslf so much for Zen3.I think it's safely bet that Zen5 has larger realworld IPC uplift than Zen2-Zen3 iteration at least in FP performance

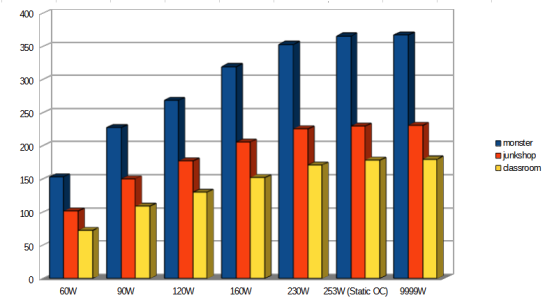

Blender 3.3 is a relatively moderate Cac workload to draw any conclusionsLooks like 9950X does not have any sweet spot for perf/watt. It keeps gobbling up any additional Watts given and turns it into perf.

The global frequency limit is not a static metric*, look at any of the 7950X/X3D HWInfo screenshots running Blender. IIRC L3 limits are not taken into account when calculating it, so the actual effective clocks are often below the global frequency limit.Hmm. Still don't really know what you mean.

Global limit is 5.85 GHz, same as the 7950x. The L3 cache runs at the same frequency as the cores for Ryzen CPUs, so there's no separate limit.

Blender 3.3 is a relatively moderate Cac workload to draw any conclusions

The global frequency limit is not a static metric*, look at any of the 7950X/X3D HWInfo screenshots running Blender. IIRC L3 limits are not taken into account when calculating it, so the actual effective clocks are often below the global frequency limit.

But my point was just that HWInfo reporting the actual Global Frequency limit wrong on that Zen5 PC (in fact it's reporting CCLK limit instead)

------------

* it's aggregated by PID controller from a set of actual individual infrastructure and other limits

It was already proper solder.especially if they've replaced whatever thing they've used with proper solder

I feel humiliated right nowa very large custom cooling rig with a optimus signature v3 block together with a MO-RA3 radiator

Hopefully, im one of the guys on OCN who had ddr4 running at 4133/2066 mhz "stable" (not that I used it for 24/7 settings, lol) and have a number of entries in the Google sheet for DDR4 overclocking (mongoled), so hope so see 2:1 running over spec on Zen5I am jealous. If I enable PBO Windows stops booting, even if i touch no other settings.

Changing anything except curve optimizer is futile.

AMD said the chips run cooler. Zen 4 will run cooler if you tweak it. Enabling CO alone dropped my chip 10 degrees with a slight performance uplift.

Zen 4 can do it as well, you just need a recent BIOS. Many on OCN have achieved it. If I had the money to burn I would pick up a better kit that could handle 8000, because mine only does DDR5-6200. Alas I currently have other priorities.

It's just the thermal superposition effect typical of multi-hotspot packages.With 10-15C variance between cores on the same CCD? It seems there were big bubbles or its application to the chiplet is very uneven.

It disappears if the substance between IHS and silicon is removed and replaced either with direct die cooler or liquid metal, so I doubt it.It's just the thermal superposition effect typical of multi-hotspot packages.

No.It disappears if the substance between IHS and silicon is removed and replaced either with direct die cooler or liquid metal

Why would someone delid an ES, especially if they are required to give it back to AMD?Delided ?