Tachyonism

Junior Member

- Jan 24, 2026

- 8

- 15

- 36

"Patent leak" lol.RGT on L1 cache pooling/sharing & reduced L2 cache & lack of infinity cache

"Patent leak" lol.RGT on L1 cache pooling/sharing & reduced L2 cache & lack of infinity cache

so the question is what did they hope to achieve in these 6 months of H1-2026Yes, that’s correct. LLVM has a roughly 6-month release cycle. If AMD misses contributing or integrating for one release, the next official release opportunity would be about 6 months later. So missing a deadline can introduce a half-year delay for official inclusion.

Perfecting drivers? Only I don't think they committed anywhere near the stuff for this, maybe it's just somebody to collect bonus for shipping LLVM enablement on time and budget.Some testing of hardware ?? why does that need LLVM updates ???

That's just normal compiler enablement schedules.so the target is September 2026 ???

Yup patents (see next post) confirm.Well gfx13+ are TBIMR

Seems like AMD's implementation is more advanced.As is everything Nvidia since Maxwell.

You're still have no real tile storage (or a real tiler) to distribute screenspace across.

IDK if it's true TBIMR but looks improved.It's entirely possible AMD's tiling/binning still isn't on Nvidia's level and that AMD won't have true TBIMR until gfx13.

It does look promising, but I can only repeat what the patents say (see next post), not what it means and what the implications are.If gfx13 makes good improvent towards a (better) TBIMR we could expect decent efficiency gains (energy and memory bandwidth).

Isn't that the old news regarding chiplet based GPUs?TLPBB a thing?

There's also another rendering pipeline efficiency boosting effort called TLPBB (Two-Level Primitive Batch Binning) that has five public patents but won't list these here unless Kepler confirms.

Seems like the new TLPBB patents expand on the underlying idea significantly and has been modified to enhance the TBIMR pipeline. But as a standalone thing in general it seems to achieve the same goal: reduce unneccessary computations and memory bandwidth usage.Isn't that the old news regarding chiplet based GPUs?

As far as I understand TLPBB and TBIMR could be combined.

More like the death of Moore's Law for caches and memory. PHY/analog scaling died multiple gens ago done and cache scaling is moving at snail pace rn.All market players agree that memory bandwidth and data movement (energy efficiency) is the one major concern regarding making chips faster (besides of slowed down Moore's Law). So developing technologies or at least enhancements of existing stuff with such a focus makes very much sense (TBIMR, TBDR, TLPBB, shared L0/L1 caches, universal compression, ...).

posted on pantherlake thread with more detail,

you can get Halo 392 full laptop 'ASUS TUF' for around 1500 bucks now

pantherlake machines START from 1500, up to 2500. DOA

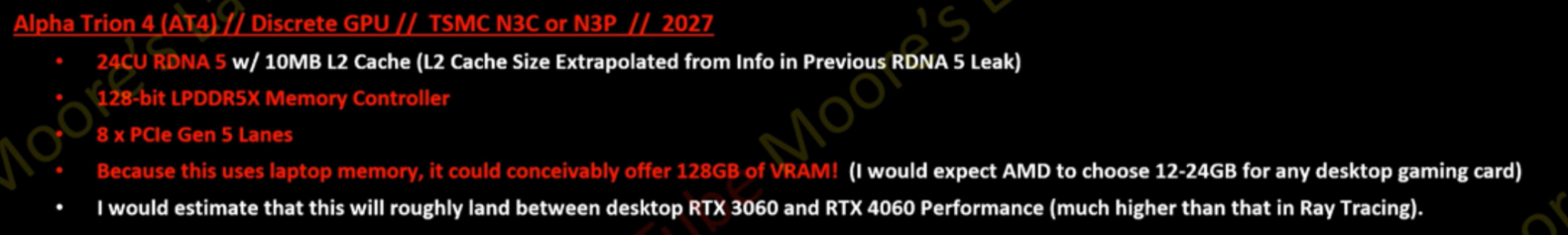

AT4 obliterates the gabecube, not to mention the CPU delta.what will be the price of a medusa premium NUC ? (It is effeectively the specs of a 2027 steam machine)

Whatever RTX6050 laptops will be targeting -$100.what will be the price of a medusa premium NUC ?

If so then wont people just buy the 6050 laptop, since AT4 is expected to be between 3060 and 4060 only? According to you, the Medusa Premium (AT4) would come with a premium pricing, whereas the 6050 is just a bottom-tier chip.Whatever RTX6050 laptops will be targeting -$100.

They're discrete compete parts, 45/85W respectively.

AMD's plan could well be to run ROCM on medusa premium & hawk it for $1500 — until open AI goes bankruptDepending on clock rates, IPC uplift and bandwidth efficiency of RDNA5, I expect the upper performance ceiling of AT4 to be at around RX 9060 / RTX 5060 and maybe even 9060 XT level. 24 vs. 28/32 CU. With the additional benefit, that AT4 is not a 8GB GPU

I am talking about desktop performance levels here (and AT4 in that form factor as well). AT4 in mobile form factor will be slower, so 4060 desktop might be a good guess.

Yeah 9060 XT perf at desktop power levels should be possible. For Medusa Premium it would be lower due to power limits and also sharing mem BW with CPU.Depending on clock rates, IPC uplift and bandwidth efficiency of RDNA5, I expect the upper performance ceiling of AT4 to be at around RX 9060 / RTX 5060 and maybe even 9060 XT level. 24 vs. 28/32 CU. With the additional benefit, that AT4 is not a 8GB GPU

I am talking about desktop performance levels here (and AT4 in that form factor as well). AT4 in mobile form factor will be slower, so 4060 desktop might be a good guess.

who said that.since AT4 is expected to be between 3060 and 4060 only

6050 starts at above-kilobuck laptops usually.According to you, the Medusa Premium (AT4) would come with a premium pricing, whereas the 6050 is just a bottom-tier chip.

Unless RDNA4 has TBB and TLPBB it looks like Xclipse 960 maybe exceeds baseline and could have some significant customizations. From LinkedIn:All market players agree that memory bandwidth and data movement (energy efficiency) is the one major concern regarding making chips faster (besides of slowed down Moore's Law). So developing technologies or at least enhancements of existing stuff with such a focus makes very much sense (TBIMR, TBDR, TLPBB, shared L0/L1 caches, universal compression, ...).

Samsung also filed patents for TBB and TLPBB.• Worked on the PBB (Primitive Batch Binning) module

Increases cache hit rate by using the spatial locality across primitives in a given screen space

• Worked on Two-Level PBB (TLPBB) – a mobile GPU-friendly feature

MLID, that's the only source I have. If you have better source, show it.who said that.

$1000 is still mid-range pricing (and even low-tier pricing for gaming laptops). If it's something "premium pricing", I imagine it to be $1500, and in that price bracket, you should be able to get a xx60 laptop too.6050 starts at above-kilobuck laptops usually.

How is that possible with only one SE (AT4) vs two SEs (Navi 44)? More ROPs and bigger Rasterizer?Yeah 9060 XT perf at desktop power levels should be possible. For Medusa Premium it would be lower due to power limits and also sharing mem BW with CPU.

That's not mid-range at all.$1000 is still mid-range pricing (and even low-tier pricing for gaming laptops).

$1500 is the upper tiers start already.If it's something "premium pricing", I imagine it to be $1500, and in that price bracket

Depends on the chassis.you should be able to get a xx60 laptop too.

Modern games are rarely ROP-limitedHow is that possible with only one SE (AT4) vs two SEs (Navi 44)? More ROPs and bigger Rasterizer?

If true then Navi 44 -> 48 extrapolation suggests AT3 dGPU = ~9070 - 9070XT.

Guess AT2 dGPU ~4090 is also possible?

Assumed it had an impact due to poor 9070 -> 9070XT perf scaling is in raster games. ~12% at 4K according to TPU. That's only half of ~25% compute gain (based on TPU avg. game clock).Modern games are rarely ROP-limited