Kinda makes you wish Intel and AMD would just license SVE2 from ARM and roll with that instead.

They don't have to license RVV from the RISC-V Foundation. They can just yoink it and slap a prefix like RVEX(alternate isa encapsulation) and say it has similar properties as RVV. Which in turn RVV 1.0~2.0 has a upper-limit of 65536-bit vectors, with a defined limit of 4096-bit.

AVX512/AVX10 still has L'L 11 for 1024-bit reserved. Needs a second instructions set like AMX to get matrix, with different registers.

SVE caps out at 2048-bit and needs SME to get more utility.

RVV does both SVE/SME and gives a upper limit of 65536-bit. Anyone can take the RVV spec and modify it for their own architecture.

Intel's partnership with SiFive with the above means they can technically do two things.

- Gut x86 and loan E-cores to SiFive

- Have SiFive and themselves develop toolchains to support RVV-x86-64(Intel's distribution of E-cores) and RVV-rv64(SiFive's distribution of Intel E-cores). I don't see them doing P-core licensing with future forest and future lake-n processors.

A microprocessor natively translates and executes instructions of both the x86 instruction set architecture (ISA) and the Advanced RISC Machines (ARM) ISA. An instruction formatter extracts distinct ARM instruction bytes from a stream of instruction bytes received from an instruction cache and...

patents.google.com

https://en.wikipedia.org/wiki/Alternate_Instruction_Set

Just a reminder, almost everyone in this patent and the makers of AIS is at Intel.

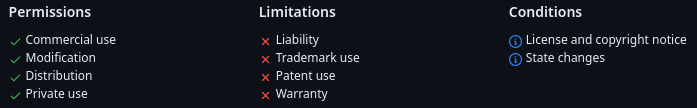

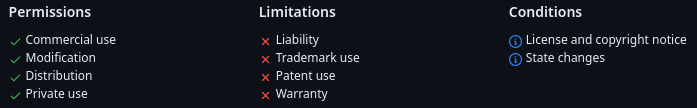

Also, Intel is already a premier member of the RISC-V foundation. So, in fact they are already licensing RVV officially. => "Use of RISC-V Trademark (name and/or logo) for commercialization" If they take RVV smoosh it into x86 isa, they can use the RISC-V trademark.

www.tomshardware.com

www.tomshardware.com