Yeah, makes sense for Xeon E without graphics.

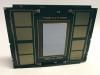

Summary so far: Each 4x4 grid SPR tile has 15 cores, 32 Gen5 PCIe and 2 DDR5 memory channel support. SPR Xeon products:

1 tile: LGA1700 (Xeon E)

2 tiles or a bigger (e.g. 5x5) grid tile: HEDT socket (Xeon W)

4 tiles: LGA4677 (Xeon Scalable)

EMR will likely have support for 5x5 grid tiles. The size of the tiles and hence the number of cores is gated by the power consumption. Let’s see if by next year Intel 7 process will be further refined to address this.

There's one flaw in that analysis. With Alderlake, all you need is a compatible chipset for ECC support, which is a departure from previous generations.

Process doesn't have to be refined, as if the struggles with Sapphire Rapids are true, then the design and the core itself has lots of room for refinements. A good quality silicon can result in both lower power consumption and/or higher clock speeds, even if the process is exactly equal.

Thats exactly why i think its not that far-fetched idea, even though MLID is not exactly the most trusted source.

But then again, as a simple layman, i admit to have no real clue.

MLID has been nearly 100% accurate with Intel leaks. Don't know if he got any wrong which is why I say "nearly".

Yes we can't say they haven't made additional core configurations for Sapphire Rapids. That's very interesting. If they can get a 96 core version out with Emerald Rapids, it doesn't look as catastrophic, compared to previous rumors of being ending at 64 cores.

At 96 cores though, we might be seeing 4x 550mm2 tiles. Surely they don't seem to be taking advantage of tiles to reduce costs at all lol.

Problem with that is segmentation.

Be it monolithic or 2xchiplets then there's only 4 memory channels for the socket which is a marketing problem for bronze/silver xeons.

Not sure if that's necessarily a problem for a marketing point of view. It just gives them more flexibility. Before it was stuck with certain number of memory channels because of the way it's designed. Now you can segment them further. Kinda a wet dream for marketing.

You would think if they were capable of making a Larger compute tile with 24 cores that had quad channel memory, they would use it on the Top of the line Sapphire Rapids and charge $20,000 for it.

MLID(who has nearly perfect record with Intel leaks

by the way) is talking about the 24-core 5GHz SPR part having anywhere between 200 to 300W TDP. One would think quadrupling that would cause issues. Can anyone guess where that might be?