The Skylake mobile chip, Core i7 6700HQ is a quadcore with a base clock of 2.6GHz at 45w. All core boost is 3.1GHz. So this upcoming Tigerlake chip essentially doubles the cores, and has a +500MHz base clock and about 20% ipc bump at the same power. Where the 6700HQ has a single core boost of 3.5GHz, this chip should be hitting 5GHz.It looks like the 8 core Tigerlake has a base clock of 3.1 at 45W but it only has 32 EUs compared to the 1185G7's 96EU.

Is there a reason for BGA devices to have more pins than the LGA variants? 6700K / 1151 and the 6820HK / 1440 etc

-

We’re currently investigating an issue related to the forum theme and styling that is impacting page layout and visual formatting. The problem has been identified, and we are actively working on a resolution. There is no impact to user data or functionality, this is strictly a front-end display issue. We’ll post an update once the fix has been deployed. Thanks for your patience while we get this sorted.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Discussion Intel current and future Lakes & Rapids thread

Page 315 - Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.

Supply limited I guess, but if given a higher power envelope, seems like a better desktop chip than RL.The Skylake mobile chip, Core i7 6700HQ is a quadcore with a base clock of 2.6GHz at 45w. All core boost is 3.1GHz. So this upcoming Tigerlake chip essentially doubles the cores, and has a +500MHz base clock and about 20% ipc bump at the same power. Where the 6700HQ has a single core boost of 3.5GHz, this chip should be hitting 5GHz.

uzzi38

Platinum Member

No, there's a bigger problem preventing TGL-H from coming to desktop. It's definitely not yields nor is it supply.

And no it's not clocks nor anything wrong architecturally preventing the die from being used on desktop. If Intel wanted they could totally have TGL-S, they are actively choosing not to.

And no it's not clocks nor anything wrong architecturally preventing the die from being used on desktop. If Intel wanted they could totally have TGL-S, they are actively choosing not to.

coercitiv

Diamond Member

No, there's a bigger problem

One of these contradicts the other.If Intel wanted they could totally have TGL-S

SAAA

Senior member

Reason being? They want Alderlake to make a bigger splash? Need the capacity for servers now?No, there's a bigger problem preventing TGL-H from coming to desktop. It's definitely not yields nor is it supply.

And no it's not clocks nor anything wrong architecturally preventing the die from being used on desktop. If Intel wanted they could totally have TGL-S, they are actively choosing not to.

Not that I particularly disagree, considered an 8 core TGL with only 32EU is probably not that bigger than quad cores they are selling now, even in relatively cheap laptops, so indeed it isn't clocks or yield.

uzzi38

Platinum Member

Nah, not really. It's a problem that doesn't affect TGL-H if the chip existed in a vacuum with Intel doing nothing else for the rest of the year. TGL-H is just later than most people expect. So late that it's just not worth bringing to desktop at all, because ADL-S will be a thing not-too-long-after.One of these contradicts the other.

At this point I'm just sincerely hoping that this is the last delay to 10nm products we hear of, but unfortunately I'm not certain of it.

TGL-H is just later than most people expect.

Which is presumably because of the yields.

Reason being? They want Alderlake to make a bigger splash? Need the capacity for servers now?

Not that I particularly disagree, considered an 8 core TGL with only 32EU is probably not that bigger than quad cores they are selling now, even in relatively cheap laptops, so indeed it isn't clocks or yield.

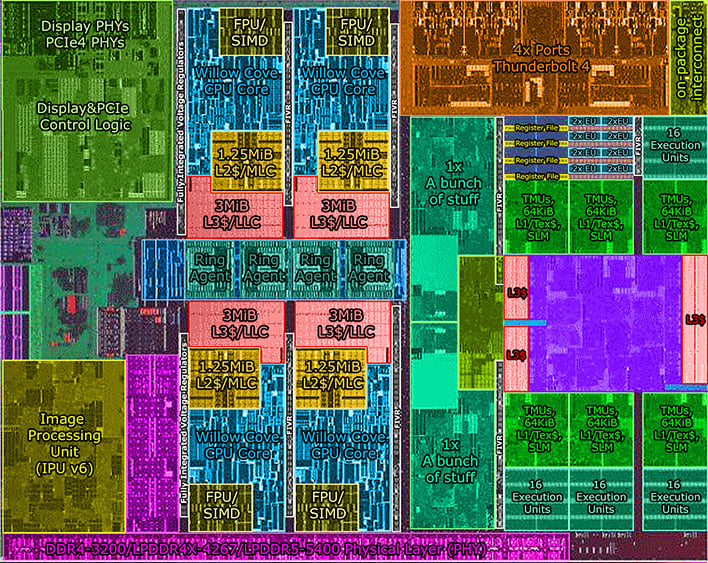

The EUs don't take up too much space. Now what does is the IPU and the Thunderbolt; Intel's removed that on H in the past. But if both are there you are looking at a decent increase in size.

uzzi38

Platinum Member

Which is presumably because of the yields.

Won't pretend I for sure know the reason why, but the yields argument doesn't make sense. TGL-H would be a very similar die to TGL-U in size and clocks in early 2021 probably won't be a big enough issue either. I mean, 4.8GHz is doable now after all.

SAAA

Senior member

Which is presumably because of the yields.

The EUs don't take up too much space. Now what does is the IPU and the Thunderbolt; Intel's removed that on H in the past. But if both are there you are looking at a decent increase in size.

The EUs might not be large, but why bother reducing them to a third then?

I see enough space for two more cores using that cache/EU area and moving things around a bit, then the whole dice might get ~15% larger adding another column for two more cores. So 8 cores and 32EUs + full IPU and thunderbolt in a 165 mm^2 die rather than 144 mm^2.

Doesn't sound that hard to yield if they are planning hundreds of mobile systems with millions of chips on the first one.

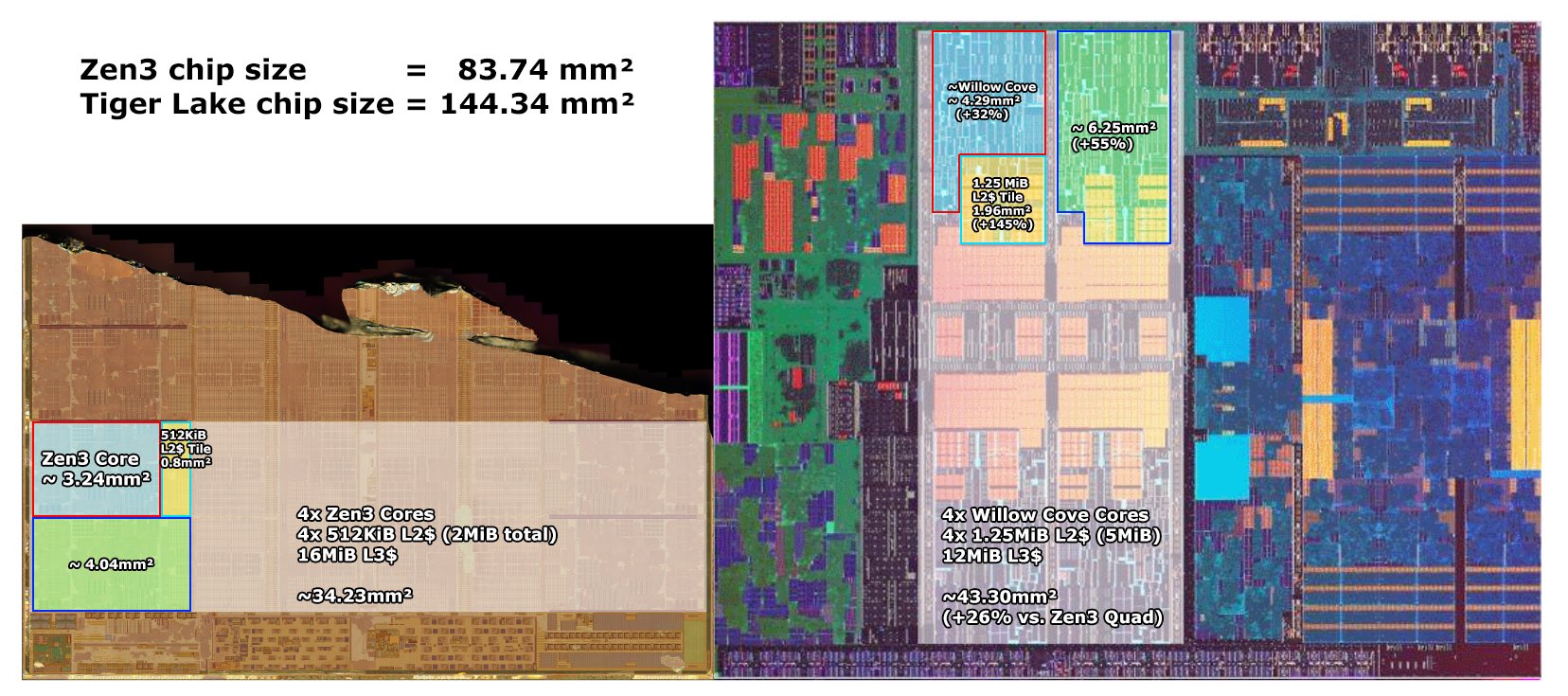

Sidenote, someone is looking into cores themselves for comparison:

Shows that Intel cores are somewhat larger with comparable IPC, caches too. Hopefully helps with 5+ GHz clocks, but they have to strive for denser designs. That 7nm has to work or they'll need TSMC for a while/permanently.

IntelUser2000

Elite Member

Is there a reason for BGA devices to have more pins than the LGA variants? 6700K / 1151 and the 6820HK / 1440 etc

Integrated PCH?

Can't be just the PCH. The Y-chips have more balls than U-chips. Something to do with power delivery. Since the mobile chips have to reach really low standby power and even lower C-states, the extra connections might help in doing that.

Did they ever port the SF features for Rocketlake too? The power draw wouldn't be significantly higher, right? Cfv^2 = watts?

Nope. SF features are for 10nm. They could do that for 14nm, but that means investing in a node that's designed to be obsolete soon.

Combination of excessive power use and even die size due to the larger/wider core is why they have only 8 cores. It's supposed to use 200-250W just like the 10900K, despite having 2 less cores.

. . . that might be true, but I see no reason why Intel would even think about Sunny Cove on 10SF (or 10SFE).

They could have Tigerlake-S, but I suspect even on 10nm SF it can't reach the crazy 5.3GHz+ frequencies they are aiming for, since 14nm cores have reached that due to endless refinement. If the best case frequency they can pump out is 5GHz, then the improved uarch will be significantly countered by the loss in frequency.

A 5 vs 5.3GHz its a 6% difference. 5.4GHz is 8%. That's already half of gains due to architecture lost.

The EUs might not be large, but why bother reducing them to a third then?

Shows that Intel cores are somewhat larger with comparable IPC, caches too. Hopefully helps with 5+ GHz clocks, but they have to strive for denser designs. That 7nm has to work or they'll need TSMC for a while/permanently.

You can actually see from the shot that to cut area taken by the Xe iGPU to half, you need to cut 64EUs away. The performance won't go down to a third, since fixed function units and bandwidth stay the same. If equal, the 96EU version is going to be 2-2.5x faster, but desktops aren't thermally limited so we might end up with a figure close to half the performance.

Their Tremont cores are extremely dense. It took 4x Goldmont cores to equal single Skylake. It takes 5x Tremont cores for a single Sunny Cove core. The size of the core in Tremont is only slightly larger than the 512KB L2 cache in Zen 3.

I suspect this is part of the reason they are planning hybrid, as the existence of the two nicely bridges the differences.

The only issue is that servers are left hanging. They might just need a dedicated third core that's based on the Core uarch but focuses on 4GHz frequencies for higher densities.

Last edited:

Can't be just the PCH. The Y-chips have more balls than U-chips. Something to do with power delivery. Since the mobile chips have to reach really low standby power and even lower C-states, the extra connections might help in doing that.

IIRC, the bump pitch is significantly smaller for the Y series chips. Probably translates to much lower current limits per bump -> more bumps needed for adequate power delivery. Y has less IO pinout than U, so power delivery is the only sane explanation.

They could have Tigerlake-S, but I suspect even on 10nm SF it can't reach the crazy 5.3GHz+ frequencies they are aiming for, since 14nm cores have reached that due to endless refinement. If the best case frequency they can pump out is 5GHz, then the improved uarch will be significantly countered by the loss in frequency.

5.3GHz is probably possible. 4.8 is what they can achieve within U series power limitations. Think it could probably get up to 5GHz with a bit more power. Then ULT vs XLT is another 5% or so.

The only issue is that servers are left hanging. They might just need a dedicated third core that's based on the Core uarch but focuses on 4GHz frequencies for higher densities.

At the rate that Atom's scaling relative to Core, a middling architecture derived from the latter doesn't make much sense.

IntelUser2000

Elite Member

IIRC, the bump pitch is significantly smaller for the Y series chips.

Good point.

5.3GHz is probably possible. 4.8 is what they can achieve within U series power limitations. Think it could probably get up to 5GHz with a bit more power. Then ULT vs XLT is another 5% or so.

Personally I'm betting it'll be 100-200MHz less, because they bothered to release a backport. Any clock speed regressions are going to show compared to Cometlake.

Because its strange that a much smaller die size and lower TDP seems like an easy decision to use Tigerlake-H as the base. Instead, just for the -S its going to end up with a backport.

@SAAA I took another look at the Tigerlake die and if they cut the GPU to 32EUs, and the Thunderbolt portion to 2x, the same chip will end up being 115mm2. With 8 cores, it'll be 156mm2. That's not even taking out the IPU. They might be able to get it under 150mm2(It won't be a straight reduction as it still needs to fit within the rectangular shape.

An alternative is a "Cypress Cove" in 10nm. Basically, Icelake but using the 10nm SF process.

At the rate that Atom's scaling relative to Core, a middling architecture derived from the latter doesn't make much sense.

I'm hoping Golden Cove does better in performance and/or core size. The leaks/rumors don't inspire any confidence though.

Hulk

Diamond Member

Look how is that going in real life, or Intel 6/12 vs AMD 6/12 CPU king of today Desktop market.

Intel CPU is cheeper, but hm 99% people buy only R5 3600.

Intel Core i5 10400F 6x 2.90GHz So.1200 TRAY - Sockel 1200 | Mindfactory.de

INTEL Desktop von Intel | Intel Core i5 10400F 6x 2.90GHz So.1200 TRAY :: Verfügbar :: über 320 verkauft :: 24 Jahre Kompetenz | Hier bestellenwww.mindfactory.de

Intel Core i5 10400 6x 2.90GHz So.1200 BOX - Sockel 1200 | Mindfactory.de

INTEL Desktop von Intel | Intel Core i5 10400 6x 2.90GHz So.1200 BOX :: Lagernd :: über 2.320 verkauft :: 24 Jahre Kompetenz | Hier bestellenwww.mindfactory.de

Suche nach ''i5 10400'': 25 Treffer | Mindfactory.de

Es wurden 25 Artikel gefundenwww.mindfactory.de

AMD Ryzen 5 3600 6x 3.60GHz So.AM4 BOX - Sockel AM4 | Mindfactory.de

AMD Desktop von AMD | AMD Ryzen 5 3600 6x 3.60GHz So.AM4 BOX :: Bestellt :: über 125.370 verkauft :: 24 Jahre Kompetenz | Hier bestellenwww.mindfactory.de

R5 3600, 103 000 sold

i5 two versions, 800 sold

"Rocket Lake 8/16 CPU estimated sales", Intel 2 vs AMD 8/16 CPU 20 units no doubt.

Ouch! Yes, can't really argue with those numbers except to say if Intel want to sell parts they are going to have to continue to drop prices until they find the market. And then have to hope they can still turn a profit at the strike price. As I wrote above, the parts have to be "somewhat competitive" performance-wise and I'll add very competitive from a pricing point-of-view.

Because its strange that a much smaller die size and lower TDP seems like an easy decision to use Tigerlake-H as the base. Instead, just for the -S its going to end up with a backport.

Do keep in mind that Rocket Lake is dirt cheap to produce. Even if there are no 10nm volume concerns, Rocket Lake might still be the more economic choice for the desktop.

@SAAA I took another look at the Tigerlake die and if they cut the GPU to 32EUs, and the Thunderbolt portion to 2x, the same chip will end up being 115mm2. With 8 cores, it'll be 156mm2. That's not even taking out the IPU. They might be able to get it under 150mm2(It won't be a straight reduction as it still needs to fit within the rectangular shape.

I won't give a number, but some more things to consider in your calculations.

+ more PCIe, - some media support/performance.

I'm hoping Golden Cove does better in performance and/or core size. The leaks/rumors don't inspire any confidence though.

Performance, yes. Core size.......

IntelUser2000

Elite Member

Do keep in mind that Rocket Lake is dirt cheap to produce. Even if there are no 10nm volume concerns, Rocket Lake might still be the more economic choice for the desktop.

I get the economics part. I cannot see how it justifies as a product. You can see from the leaked information from Sharkbay the 8 core Rocketlake having same IccMax as the 10 core Cometlake parts. Overall I think a slightly lower clocked Tigerlake-S would have ended up being better. 5GHz Willow Cove is still faster in ST than 5.3GHz Skylake. Look how much the Zen 3 got! Architecture is more important than clocks for games.

My belief is that its a combo of not being able to get Tigerlake-S out by early Q1, and seeing how bad it is looking from outside, one can imagine how chaotic it is inside. Similar to not having any 6 core Tigerlake-U parts.

I won't give a number, but some more things to consider in your calculations.

+ more PCIe, - some media support/performance.

You can do all that with few mm2 differences. They already have empty space in their products, due to the way it is designed(easy proliferation). Media changes will be minimal when you think in terms of size.

Performance, yes. Core size.......

What I mean by that is if the performance gains are big enough the Core size can be justified. Scalar gains in CPUs are nonlinear. Sunny Cove had to grow significantly, and way above the 15-20% gain. It was 38% if I'm not mistaken? If say Golden Cove is 20% faster with 15% larger core, then they are on the right track. Or if its 30% larger but is 35% faster.

Last edited:

What I mean by that is if the performance gains are big enough the Core size can be justified. Scalar gains in CPUs are nonlinear. Sunny Cove had to grow significantly, and way above the 15-20% gain. It was 38% if I'm not mistaken? If say Golden Cove is 20% faster with 15% larger core, then they are on the right track. Or if its 30% larger but is 35% faster.

I get what you meant. I'm just implying not to get your hopes up for even a linear performance/area ratio. Though personally I think power is a much bigger issue with Core right now than area.

IntelUser2000

Elite Member

I get what you meant. I'm just implying not to get your hopes up for even a linear performance/area ratio. Though personally I think power is a much bigger issue with Core right now than area.

What you are saying is the Atom cores will soon grow to a point where the extra die/power use won't be worth the extra performance gained with Core.

I can agree with this, however,

I'm suggesting an alternative, where if Core is significantly behind, why can't it be improved? Is it that hopeless just in terms of design, nevermind process?

Asterox

Golden Member

Ouch! Yes, can't really argue with those numbers except to say if Intel want to sell parts they are going to have to continue to drop prices until they find the market. And then have to hope they can still turn a profit at the strike price. As I wrote above, the parts have to be "somewhat competitive" performance-wise and I'll add very competitive from a pricing point-of-view.

R5 3600 is best seling CPU on Mindfactory, or today global best seling Desktop CPU.

What is Intel best seling CPU on Mindfactory? Old i7 6700K sold about 46 000 units.No other new or newer Intel CPU has sold more units.

Intel Core i7 6700K 4x 4.00GHz So.1151 WOF - Sockel 1151 | Mindfactory.de

INTEL Desktop von Intel | Intel Core i7 6700K 4x 4.00GHz So.1151 WOF :: über 46.140 verkauft :: 24 Jahre Kompetenz | Hier bestellen

Intel Core i7 8700K 6x 3.70GHz So.1151 WOF - Sockel 1151 | Mindfactory.de

INTEL Desktop von Intel | Intel Core i7 8700K 6x 3.70GHz So.1151 WOF :: Lagernd :: über 28.830 verkauft :: 24 Jahre Kompetenz | Hier bestellen

What you are saying is the Atom cores will soon grow to a point where the extra die/power use won't be worth the extra performance gained with Core.

I can agree with this, however,

I'm suggesting an alternative, where if Core is significantly behind, why can't it be improved? Is it that hopeless just in terms of design, nevermind process?

Oh, Core can be improved and needs to for it to have any future. I'm just saying that the redesign it needs isn't happening with Golden Cove. Nor Redwood Cove, for that matter.

I saw the Moore's Law is Dead episode of the Redwood Cove leak/rumor but the Alder Lake SKU's dont make sense to me.

Personally I'm thinking in each segments (i9/i7/i5/i3) there will be a distinction between k and non-k not just in clocks and overclocking but in secondary cores to further bifurcate the product line-up.

So the product line-up could look like this:

i9K 8HT+8 (24T) 5.5 GHz*

i9 8HT+6 (22T) 5.4 Ghz

i7K 8HT+4 (20T) 5.3 Ghz

i7 8HT+2 (18T) 5.2 Ghz

i5K 6HT+4 (16T) 5.1 Ghz

i5 6HT(12T) 5.0 Ghz

[i3K 5HT (10T) 4.9 GHz]* *

i3 4HT (8T) 4.8 GHz

PT 4ST (4T) 4.6 Ghz

* 5.5 GHz is based on the yearly cadence of the last 3/4 years where they bumped the max. speed with 0.1 GHz each year. Obviously if it turns out lower everything will be bumped down accordingly.

**i3K doesn't exist anymore with Comet Lake but I think it would be a great value product for low-budget enthusiasts/gamers. 5 core is unusual but would be a good filler in what otherwise would be a pretty big gap between i5 and i3.

Personally I'm thinking in each segments (i9/i7/i5/i3) there will be a distinction between k and non-k not just in clocks and overclocking but in secondary cores to further bifurcate the product line-up.

So the product line-up could look like this:

i9K 8HT+8 (24T) 5.5 GHz*

i9 8HT+6 (22T) 5.4 Ghz

i7K 8HT+4 (20T) 5.3 Ghz

i7 8HT+2 (18T) 5.2 Ghz

i5K 6HT+4 (16T) 5.1 Ghz

i5 6HT(12T) 5.0 Ghz

[i3K 5HT (10T) 4.9 GHz]* *

i3 4HT (8T) 4.8 GHz

PT 4ST (4T) 4.6 Ghz

* 5.5 GHz is based on the yearly cadence of the last 3/4 years where they bumped the max. speed with 0.1 GHz each year. Obviously if it turns out lower everything will be bumped down accordingly.

**i3K doesn't exist anymore with Comet Lake but I think it would be a great value product for low-budget enthusiasts/gamers. 5 core is unusual but would be a good filler in what otherwise would be a pretty big gap between i5 and i3.

What I mean by that is if the performance gains are big enough the Core size can be justified. Scalar gains in CPUs are nonlinear. Sunny Cove had to grow significantly, and way above the 15-20% gain. It was 38% if I'm not mistaken? If say Golden Cove is 20% faster with 15% larger core, then they are on the right track. Or if its 30% larger but is 35% faster.

Not sure where you got your optimism from. If there would be a low hanging fruit, which over-proportionally increases performance with respect to area, it would have long being taken. Thing is, in the bigger picture it gets increasingly expensive to increase (single core) performance.

LightningZ71

Platinum Member

Yo idea breaks a fundamental that has existed with the I series for many years, all processors of the same i# level have the same number of threads. The differentiator is how fast they run them, if they having working iGPUs, and power rating.I saw the Moore's Law is Dead episode of the Redwood Cove leak/rumor but the Alder Lake SKU's dont make sense to me.

Personally I'm thinking in each segments (i9/i7/i5/i3) there will be a distinction between k and non-k not just in clocks and overclocking but in secondary cores to further bifurcate the product line-up.

So the product line-up could look like this:

i9K 8HT+8 (24T) 5.5 GHz*

i9 8HT+6 (22T) 5.4 Ghz

i7K 8HT+4 (20T) 5.3 Ghz

i7 8HT+2 (18T) 5.2 Ghz

i5K 6HT+4 (16T) 5.1 Ghz

i5 6HT(12T) 5.0 Ghz

[i3K 5HT (10T) 4.9 GHz]* *

i3 4HT (8T) 4.8 GHz

PT 4ST (4T) 4.6 Ghz

* 5.5 GHz is based on the yearly cadence of the last 3/4 years where they bumped the max. speed with 0.1 GHz each year. Obviously if it turns out lower everything will be bumped down accordingly.

**i3K doesn't exist anymore with Comet Lake but I think it would be a great value product for low-budget enthusiasts/gamers. 5 core is unusual but would be a good filler in what otherwise would be a pretty big gap between i5 and i3.

DrMrLordX

Lifer

Yo idea breaks a fundamental that has existed with the I series for many years, all processors of the same i# level have the same number of threads. The differentiator is how fast they run them, if they having working iGPUs, and power rating.

Eh? i7-8700k was 12t while i7-9700k was 8t . . . and the i7-10700k is 16t.

Yo idea breaks a fundamental that has existed with the I series for many years, all processors of the same i# level have the same number of threads. The differentiator is how fast they run them, if they having working iGPUs, and power rating.

Any way you slice it this will not be the case with Alder Lake given the many different configurations tested and the rumored SKU's. So the question is rather, how to make sense of 4 tiers when there are so many different core and thread counts.

Comet Lake, whatever you might think of it, had the cleanest tiered ever (not counting the lower power versions):

10C/20T = i9

8c / 16T = i7

6c / 12T = i5

4c / 8T = i3

TBH I'd have preferred they went this route with alder lake as well.

TRENDING THREADS

-

Discussion Zen 5 Speculation (EPYC Turin and Strix Point/Granite Ridge - Ryzen 9000)

- Started by DisEnchantment

- Replies: 25K

-

Discussion Intel Meteor, Arrow, Lunar & Panther Lakes + WCL Discussion Threads

- Started by Tigerick

- Replies: 25K

-

Discussion Intel current and future Lakes & Rapids thread

- Started by TheF34RChannel

- Replies: 24K

-

-