An update with new nodes supposedly scheduled for end of the year.

Old nodes, Malta-only:

14LPe/14LPP/12LP/12LP+

New nodes to be announced, Dresden+Malta:

11LP/11LPM/12FDX

The safest assumption is 11LP/11LPM is Bulk FinFET... however, the switch from Leading Performance to Low Power might imply a full return to planar.

Example purposes:

12FDX => SHP class-node, Planar+SOI+High Mobility

11LPM => HPP class-node, Planar+Bulk+High Mobility+DDC/SSRW

11LP => SLP class-node, Planar+Bulk+DDC/SSRW

Basically all of them being 10-nm Planar Gate + 56nm minimum metal pitch

As well as potential everything being planar GAA-related:

The switch to planar impacts 3D Logic scaling, as planar-type nodes do not thermally couple as hard between logic dies.

For example rather than a Planar Monet, it is more likely to see a 3D Monet.

Top-die (high heat logic/CPU die) => Quad-core Zen('number') die

Middle-die (low heat GPU/Multimedia/Vision die) => A couple WGPs

Bottom-die (low-heat I/O die) => everything else needed.

Three small dies has nearer to linear costs rather than one gigantic planar die, etc.

However, I believe based on a couple mentions regarding LP cores from AMD on linkedin and a couple references of GloFo 12FDX at Malta:

That the 3D CCD will not be Zen but more likely derivative of Fam 16h with actual CMT2:

Shared Front-end, Split Decode, Shared Retire/Rename, Split Scheduler/Execution for Int-clusters and FP-clusters, Shared Load-Store/Bus/L2.

Same performance class as Zen, but more aggressive area/power optimization:

14nm Jaguar = 1.8 mm2

14nm Zen = 5.5 mm2

12FDX Ultra-low-power CMT2 = Less than or equal to half of 14nm Zen.

Two core/quad-cluster = ~5 mm2 and 2 MB L2 = ~ 6 mm2 = ~11 mm2 + ~11 mm2 + ~16 mm2 or smaller for 8 MB L3 => ~38 mm2.

The range for dies I got via estimation were 48 mm2 to 64 mm2, but all dies should be similar with bottom IOD being biggest, GCD mid, and CCD being smallest.

CCD+CCD+IOD = Server-orientated

CCD+GCD+IOD = Consumer-orientated

GCD+GCD+IOD = Graphics-orientated

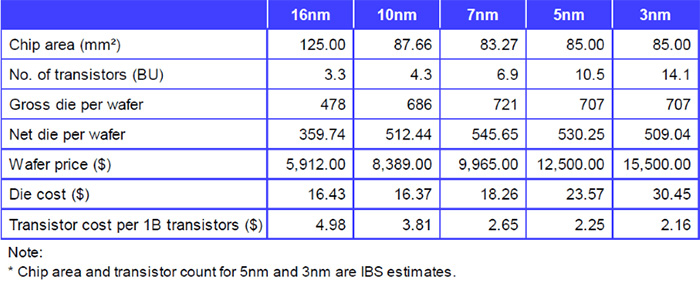

150 mm2 / $4000 (14nm/12nm FF) = 386 good dies which is greater than $12.01.

64 mm2 / $3000 (12FDX/11nm planar) = 860 good dies which needs three costs given are then greater than $10.47.

From Dual-core Zen+3 CU GCN to Quad-core Zen('number')/4 CU RDNA('number') while reducing price. With a more aggressive stance in shrinking area/power. ~51.2 mm2 / $3000 = 1096 good dies which needs three and given costs would be $8.21 which is a 0.68x drop in price just for the die.

Which means going More than Moore/3D-stacking is the clear solution if GloFo wants AMD still. It also allows AMD to reduce costs while given a more expensive node than 28nm/22nm.

NGFXShowcase:

CPU die = ~60 mm2

IOD die = ~60 mm2

CPU clock = ~4.7 GHz

CPU power = ~35W

Edit: I have a further list of approved nodes that will be launching second half 2022:

22FDX+; New Track Height (potentially, 6T or 7T)

22FDX++; Reduced CPP, same BEOL, re-uses 12FDX's new gate/SOI materials

12LP++; New Track Height (same as 22FDX+), more aggressive SDB/CNRX in standard cells.

11LP/11LPM: Low-power, Low-power+Mobility-enhancements;

Same as 12FDX but uses a local poly-crystalline layer instead of wafer length oxide under the gate(Deeply Depleted Channel/SSRW channel/etc)

The bulk hybrid layer of 12FDX should be able to 11LP transistors:

Bulk planar transistors => Low static leakage, high dynamic leakage

SOI planar transistors => High static leakage, low dynamic leakage