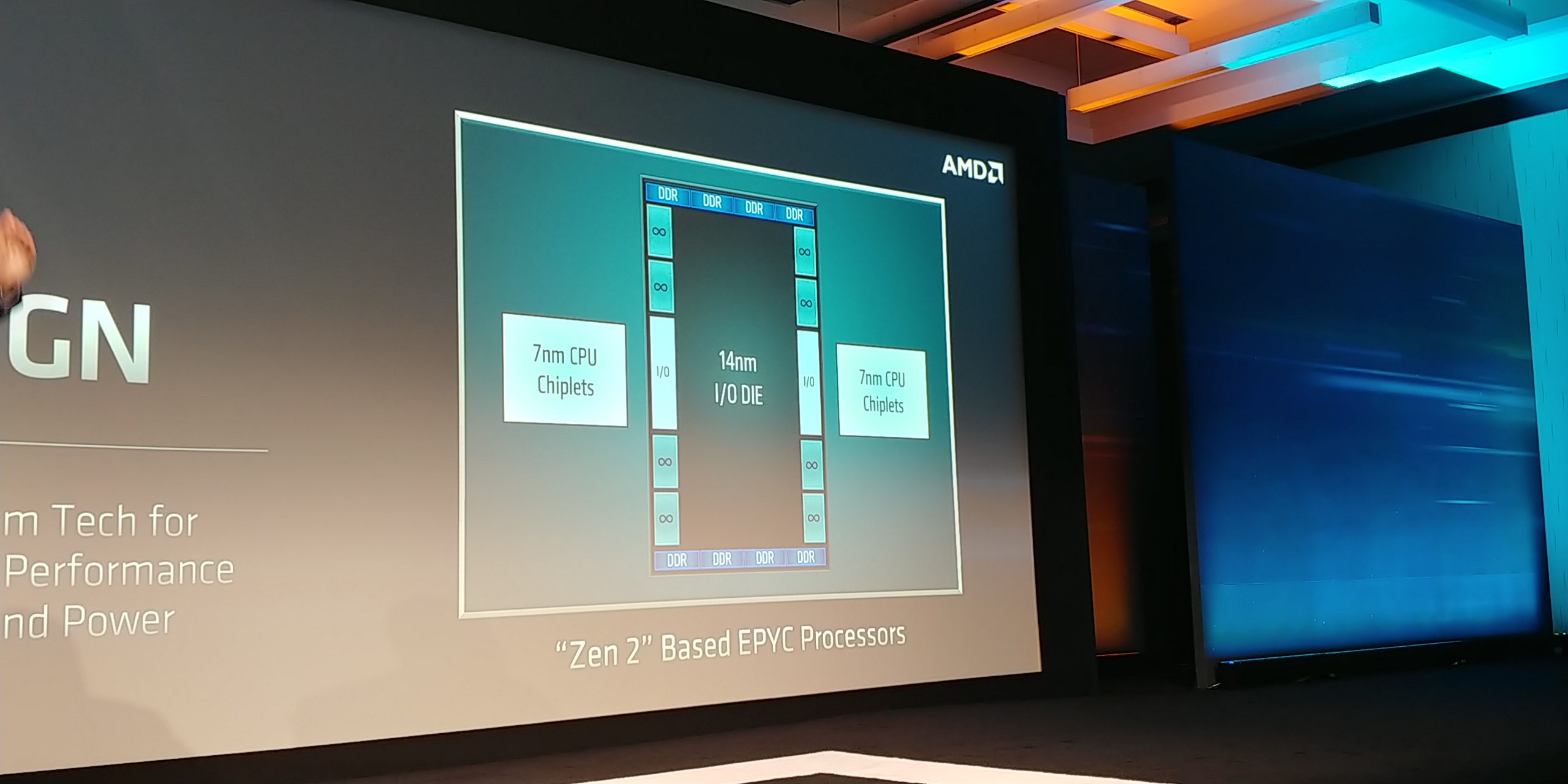

The next big question I have is how much cache does that IO die have? To host all that IO, it needs a large circumference. So a lot would fit, even at 14nm.

Hell it could 1x or 2x Zen 1 die size and it still might be a major space saver. A Normal Zen die is 190mm. Just the space saving (2x) you have it at 95mm. Take out all that IO stuff maybe you can get it down to 65mm.