adroc_thurston

Diamond Member

The bottom SKU is 6c.If that turns out to be the case, then what can be expected for the bottom SKU, e.g. 12C/24T?

The bottom SKU is 6c.If that turns out to be the case, then what can be expected for the bottom SKU, e.g. 12C/24T?

Ryzen 5 or they would bring back Ryzen 3? A Ryzen 5 with 6 cores in 2028(?) would be incredible mediocreThe bottom SKU is 6c.

idk they have a billion ways to slice up the stack.Ryzen 5 or they would bring back Ryzen 3?

I don't make the rules; TSMC does.A Ryzen 5 with 6 cores in 2028(?) would be incredible mediocre

From previous discussions in this thread, the current assumption is that Zen7 will be 32C/64T for top SKU and 16C/32T per CCX on DT.

If that turns out to be the case, then what can be expected for the bottom SKU, e.g. 12C/24T? That would map to the current case for Zen5 where we have 8C/16T for a fully working CCX, and 6C/12T for bottom SKU which is 75% of the fully working one.

To expand upon what @adroc_thurston said, that decision is made fairly late in the process as it directly impacts margins, revenue, and such. They will charge as much as possible for as little as possible. All of that will be determined based on the economy, competitors, etc. AMD is the market leader when it comes to mainstream, high performance CPUs, so expect to have to pay more for less, rather than less for more.Ryzen 5 or they would bring back Ryzen 3? A Ryzen 5 with 6 cores in 2028(?) would be incredible mediocre

From where did you get that info?There will also be 8C/16T CCD for low end.

Yeah, but if they have 16C/32T CCD as base, how many of those will have so few working cores that it’s worth binning into 6C/12T?To expand upon what @adroc_thurston said, that decision is made fairly late in the process as it directly impacts margins, revenue, and such. They will charge as much as possible for as little as possible. All of that will be determined based on the economy, competitors, etc. AMD is the market leader when it comes to mainstream, high performance CPUs, so expect to have to pay more for less, rather than less for more.

Great to see the forums back up. 🍻

I believe this was MLID leak — silver somethingFrom where did you get that info?

From previous discussions in this thread, the current assumption is that Zen7 will be 32C/64T for top SKU and 16C/32T per CCD on DT.

If that turns out to be the case, then what can be expected for the bottom SKU, e.g. 12C/24T? That would map to the current case for Zen5 where we have 8C/16T for a fully working CCD, and 6C/12T for bottom SKU which is 75% of the fully working one.

Yeah, but if they have 16C/32T CCD as base, how many of those will have so few working cores that it’s worth binning into 6C/12T?

And then onwards into 8C, 10C, 12C, 14C? And that’s only for SKUs based on single CCD. Then there will be further SKUs based on 2xCCD going onwards, so … 28C, 30C, 32C?

How many Zen7 SKUs do you expect them to have on DT?

From where did you get that info?

Yeah that was bad. Sorry for off-topic but in case my sig isn't enough, everyone please consider registering on forums.thefpsreview.com and/or anfy.ca in case of future interruptions which may or may not be permanent. Hopefully that will never come to pass, but it pays to be prepared, and having another forum to post on isn't necessarily a bad thing.Great to see the forums back up. 🍻

Same reason they have taken forever to finally push out a 2x X3D SKU.BTW, this strategy of AMD of having "Halo" product and not pairing them with V-Cache chiplet is a head scratcher and an opportunity lost.

Same reason they have taken forever to finally push out a 2x X3D SKU.

It's expense on top of expense.

The packaging required for Halo chiplets is IIRC more cost intensive compared to the "xyz Range" desktop CPU SKUs.

When you add that to X3D packaging costs as well it's a lot.

These things will never, ever be CPU-limited.BTW, this strategy of AMD of having "Halo" product and not pairing them with V-Cache chiplet is a head scratcher and an opportunity lost.

Zen6 is still a good 6-9 months from launching even assuming the RAM shortage/price hikes haven't affected the roadmap, which is optimistic at best.So it seems like problem solved in Zen 6, and then broken again in Zen 7.

Yeah they did.I doubt AMD would design a 12C CCD just to abandon it after one generation

Yeah you will, SP8 needs a 33% core density bump.hence I don't think we'll see a 16C CCD with Zen 7

Sigs don’t show up on the mobile site, just an fyi.Yeah that was bad. Sorry for off-topic but in case my sig isn't enough, everyone please consider registering on forums.thefpsreview.com and/or anfy.ca in case of future interruptions which may or may not be permanent. Hopefully that will never come to pass, but it pays to be prepared, and having another forum to post on isn't necessarily a bad thing.

Sorry for the interruption.

Indeed, they don’t.Sigs don’t show up on the mobile site, just an fyi.

Alas. I always browse in desktop mode on my phone. Or at least I think I do . . .Sigs don’t show up on the mobile site, just an fyi.

Alas. I always browse in desktop mode on my phone. Or at least I think I do . . .

Really? The mobile site works great for me.Yup. I can't do message boards on mobile unless there is no other option.

What can I say? I like a nice big monitor.Really? The mobile site works great for me.

´Works great’ is pushing it those last few days lolReally? The mobile site works great for me.

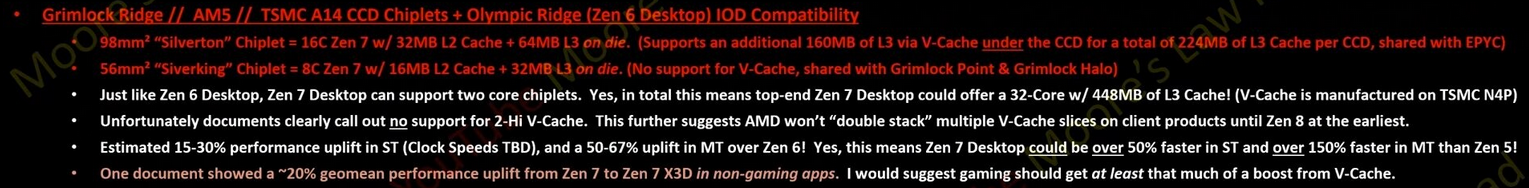

Also from that slide:MLID showed 8 core chiplets that can be added to Zen 7 Halo. So, if these chiplets exist, then they would also be used in low end desktop.

BTW, this strategy of AMD of having "Halo" product and not pairing them with V-Cache chiplet is a head scratcher and an opportunity lost.

View attachment 134974

Yeah man you don't need any of that.but not 192 MB (or 2x whatever the relevant V-Cache slice will contain) per single CCD until Zen8?