NVL is a proper tick tock combined Process+IPC double digits IPC is pretty much guaranteed like 14-18% similar to previous tocksWhile others seem to have addressed this question rather well, it seems that (for now) Intel hasn't progressed much IPC-wise with thier P cores over the last few generations. Combine that with the rumours that Nova Lake/Coyote Cove won't see major (or any) P-core clockspeed updates, and you'll have a situation where Nova Lake will struggle with ST performance (as well as MT performance, particularly in the range of 8-16 threads).

Question Zen 6 Speculation Thread

Page 307 - Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Fjodor2001

Diamond Member

- Feb 6, 2010

- 4,554

- 727

- 126

What you mentioned is also true for Zen. Remember the whole Zen 5% discussion?While others seem to have addressed this question rather well, it seems that (for now) Intel hasn't progressed much IPC-wise with thier P cores over the last few generations. Combine that with the rumours that Nova Lake/Coyote Cove won't see major (or any) P-core clockspeed updates, and you'll have a situation where Nova Lake will struggle with ST performance (as well as MT performance, particularly in the range of 8-16 threads).

Thunder 57

Diamond Member

- Aug 19, 2007

- 4,247

- 7,044

- 136

NVL is a proper tick tock combined Process+IPC double digits IPC is pretty much guaranteed like 14-18% similar to previous tocks

Tick tock hasn't been a thing for a long time now.

What you mentioned is also true for Zen. Remember the whole Zen 5% discussion?

Zen 5% was server first and did well there. Gamers and public opinion were pissed it didn't reach 32% as claimed by some.

Gaming is a low IPC Workload it's more latency and Cache sensitive...

And Intel has crap cache don't see them picking up a bunch.

Markfw

Moderator Emeritus, Elite Member

- May 16, 2002

- 27,391

- 16,233

- 136

It has been proven that Zen 5 in some tests are faster by as much as 56%.Zen 5% was server first and did well there. Gamers and public opinion were pissed it didn't reach 32% as claimed by some.

Not that is in one area, yes, so don't beat me up. but in many tests is has surpassed the 5%. I could look up the phoronix tests, but not at the moment.

DrMrLordX

Lifer

- Apr 27, 2000

- 23,180

- 13,266

- 136

NVL is a proper tick tock combined Process+IPC double digits IPC is pretty much guaranteed like 14-18% similar to previous tocks

When was the last time Intel actually made good on that? P-cores have struggled since Alder Lake.

What you mentioned is also true for Zen. Remember the whole Zen 5% discussion?

It's a meme born of some gaming benchmarks that (surprise surprise) no longer matter thanks to the 9800X3D. Meanwhile Turin says hello:

AMD EPYC 9005 Turin Turns Transcendent Performance with 768 Threads Per Server

With up to 768 threads in a dual socket server, the AMD EPYC 9005 "Turin" generation offers transcendent performance for servers

or if you prefer a desktop CPU comparison, Phoronix has something to say about it:

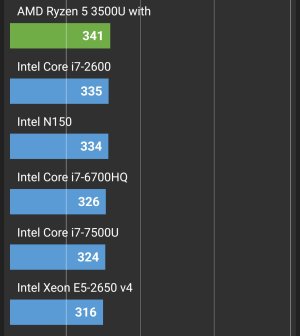

Looks more like Zen17.8%.

Tick tock hasn't been a thing for a long time now.

Yup.

Gamers and public opinion were pissed it didn't reach 32% as claimed by some.

That was due to some leakers (cough cough who could they be) going nuts on OEM numbers in server workloads.

Fjodor2001

Diamond Member

- Feb 6, 2010

- 4,554

- 727

- 126

That’s for regular Linux desktop and non-X3D, so N/A in this case.Looks more like Zen17.8%

Because the whole discussion started about the impact of bLLC, and whether NVL-S with bLLC will be able to compete with Zen6 X3D.

So what’s the real % for Zen5 gaming, if not Zen 5%?It's a meme born of some gaming benchmarks that (surprise surprise) no longer matter thanks to the 9800X3D.

ARL Fabric/LLC botched Lion Cove and SkymontWhen was the last time Intel actually made good on that? P-cores have struggled since Alder Lake.

Yup RPL had real good memory latency the L3 was okayishAnd Intel has crap cache don't see them picking up a bunch.

It has been kind of being followedTick tock hasn't been a thing for a long time now.

Intel 7 -> Intel 4/3

Golden Cove -> Redwood Cove

Gracemont -> Crestmont

N3B -> 18A

Lion -> Cougar

Skymont -> Darkmont

On TSMC Node they don't need to derisk the process causes TSMC does it for them but on their nodes they need to.

DrMrLordX

Lifer

- Apr 27, 2000

- 23,180

- 13,266

- 136

That’s for regular Linux desktop and non-X3D, so N/A in this case.

Umm okay:

Zen34%?!?

The whole discussion started about the impact of bLLC, and whether NVL-S with bLLC will be able to compete with Zen6 X3D.

And it won't, because Intel's cache is slow and adding more slow cache isn't really a good solution.

So what’s the real % for Zen5 gaming, if not Zen 5%?

Depends on the title, but:

Around 8% faster on average. Seems consistent with TPU which showed around 7.3% @ 720P:

AMD Ryzen 7 9800X3D Review - The Best Gaming Processor

The Ryzen 7 9800X3D establishes AMD as the leader in gaming performance. This Zen 5-based X3D chip is not only fast, it also comes with full support for overclocking. Besides gaming, application performance is considerably improved over the 7800X3D, but that comes at a price.

It's word soup that bears no relation to the reality of designing prime cores for Fin/NanoFlex-enabled nodes.

Well if you weren't allergic to a "wall of text" you could explain to us, in detail, where and why I'm wrong. But nope, with you, its "trust me bro". That shtick has gotten old.

Fjodor2001

Diamond Member

- Feb 6, 2010

- 4,554

- 727

- 126

Zen 7-8% is honestly not much more impressive than Zen 5%. 🤣Around 8% faster on average. Seems consistent with TPU which showed around 7.3% @ 720P:

And how do you know this will be the case for NVL-S with bLLC too?And it won't, because Intel's cache is slow and adding more slow cache isn't really a good solution.

At Computerbase.de, where they were testing different games and at 1080p instead of 720p, it was 13-14%.Zen 7-8% is honestly not much more impressive than Zen 5%. 🤣

This has been explained before, but one of the reasons is physical design.And how do you know this will be the case for NVL-S with bLLC too?

The only reason AMD can do such big L3s at such low latencies at all is the vertical stacking, because thanks to the layers being very thin, physical distance to the farthest SRAM cells doesn't increase much, despite the tripling of the total L3.

A monolithic massive 2D cache like Intels bLLC has more distance/cells to cover from corner to corner, making it much harder to get high clocks and low latency under the same hood without running into heat/power/clock/degradation issues.

The other aspect is, both vendors use exclusive cache designs nowadays, where L3 is only accessed when some data isn't found in the L2, and since Intel's P-cores have 3x as much L2 (and that extra L1.5D), they don't need to access L3 as often and as early, while also going through higher total latency before doing so (Intel's L2 has higher latency than AMD's).

Basically, Intel L3 is accessed less often for small stuff, and takes longer to access for big stuff, both by design.

Making it bigger won't improve either, that only reduces the even slower memory accesses.

Fjodor2001

Diamond Member

- Feb 6, 2010

- 4,554

- 727

- 126

Ok, but what you described was for ARL-S, I assume.

Do we know what changes will be coming for the caches in NVL-S? Are they expected to work exactly the same as in ARL-S, and if so why?

Do we know what changes will be coming for the caches in NVL-S? Are they expected to work exactly the same as in ARL-S, and if so why?

Last edited:

The only problem is L3 L2/L1 is fine if anything their L1/L2 have been pulling the weight to mitigate Slow L3And it won't, because Intel's cache is slow and adding more slow cache isn't really a good solution.

PTL has fixed the L3Ok, but what you described was for ARL-S, I assume.

Do we know what changes will be coming for the caches in NVL-S? Are they expected to work exactly the same as in ARL-S, and if so why?

DrMrLordX

Lifer

- Apr 27, 2000

- 23,180

- 13,266

- 136

Ok, but what you described was for ARL-S, I assume.

The horizontal stacking latency will apply to Nova Lake-S. Presumably the size of the L2 of Nova Lake-S will also be relevant as it is in Arrow Lake.

As far as 7-8% not being that much different . . . okay? Somehow Zen5 remains the fastest gaming CPU out there while also enjoying an impressive lead over Zen4 in everything that isn't (certain) games. Including the X3D parts where the 9800X3D has a big lead over the 7800X3D in non-gaming tasks. bLLC isn't going to solve that for Nova Lake-S, not on its own.

Last edited:

adroc_thurston

Diamond Member

- Jul 2, 2023

- 8,294

- 11,073

- 106

Castration is one way to fix it, I guess.PTL has fixed the L3

Kind of have to see whether NVL gets the fixed version or notCastration is one way to fix it, I guess.

Josh128

Golden Member

- Oct 14, 2022

- 1,509

- 2,262

- 106

adroc_thurston

Diamond Member

- Jul 2, 2023

- 8,294

- 11,073

- 106

CPU-Z is an antique memebench tho.Im sure MarkFW is about to nuke this Intel tangent in the Zen 6 thread, but new PTL CPU-z leaks show almost no IPC increase (in CPU-z) vs Raptor Lake P cores. ~165 points/GHz, base on two different runs, which match. This one is at 3GHz.

View attachment 134313

That's an ES also this config matches WCL-U 50% ST improvement over ADL-N is niceIm sure MarkFW is about to nuke this Intel tangent in the Zen 6 thread, but new PTL CPU-z leaks show almost no IPC increase (in CPU-z) vs Raptor Lake P cores. ~165 points/GHz, base on two different runs, which match. This one is at 3GHz.

View attachment 134313

This tbh it fits in L1 ...CPU-Z is an antique memebench tho.

Zen 5 x3D is significantly faster than Zen 4 x3D because they redesigned the cache so it dissipates heat more efficiently, allowing them to clock it close to the vanilla chips, which helps both gaming and productivity. Not sure the exact figures, but I think 10 to maybe even 20 percent faster for the Zen 5 x3D chips. I know AMD has tried to tweak vanilla Zen 5 for gaming, but don' know how much additional performance they were able to eek out. I think the gain for vanilla Zen 5 is still lower than 10%.That’s for regular Linux desktop and non-X3D, so N/A in this case.

Because the whole discussion started about the impact of bLLC, and whether NVL-S with bLLC will be able to compete with Zen6 X3D.

So what’s the real % for Zen5 gaming, if not Zen 5%?

As for NVL/Zen 6, I think AMD will still have a significant advantage because they will have a 12 core single CCD vCache chip. It should be an absolute beast for gaming, especially if the predictions of higher clocks pan out. NVL will be limited to a single 8 core vCache chiplet, probably w/o hyperthreading, so unfortunately, I dont see it being competitive.

Zen5 IPC:It has been proven that Zen 5 in some tests are faster by as much as 56%.

Marketing gains from +10% to +35% (average +16%)

Int gains average +13%, and FP gains average +25%.

9950X AVX512(ON) average +56%

7950X AVX512(ON) average +41%

Last edited:

9000 series X3Ds are generally the fastest gaming CPUs for now butThe horizontal stacking latency will apply to Nova Lake-S. Presumably the size of the L2 of Nova Lake-S will also be relevant as it is in Arrow Lake.

As far as 7-8% not being that much different . . . okay? Somehow Zen5 remains the fastest gaming CPU out there while also enjoying an impressive lead over Zen4 in everything that isn't (certain) games. Including the X3D parts where the 9800X3D has a big lead over the 7800X3D in non-gaming tasks. bLLC isn't going to solve that for Nova Lake-S, not on its own.

non-X3D 9000 series are about the same mean gaming performance as ARL-S counterparts. ARL-S has latency issues with ring/D2D/NGU/L3.

For NVL-S the design should be optimized for improved latency.

With same design undoubtedly 3D stacked L3 is better for latency than just horizontal increase in L3 capacity.

Regarding gaming perf, NVL bLLC versions' 144MB L3(vs the standard 36MB) should help cut memory access by a good amount which should result in decent uplift for many games relatively, though the question is how well NVL-S bLLC fares against others esp. some gaming oriented X3D SKUs in gaming and other tasks.

Thunder 57

Diamond Member

- Aug 19, 2007

- 4,247

- 7,044

- 136

9000 series X3Ds are generally the fastest gaming CPUs for now but

non-X3D 9000 series are about the same mean gaming performance as ARL-S counterparts. ARL-S has latency issues with ring/D2D/NGU/L3.

For NVL-S the design should be optimized for improved latency.

With same design undoubtedly 3D stacked L3 is better for latency than just horizontal increase in L3 capacity.

Regarding gaming perf, NVL bLLC versions' 144MB L3(vs the standard 36MB) should help cut memory access by a good amount which should result in decent uplift for many games relatively, though the question is how well NVL-S bLLC fares against others esp. some gaming oriented X3D SKUs in gaming and other tasks.

It's not just ARL that has had issues with L3. It goes back to ADL IIRC. Intel hasn't been able to fix it, as it actually got worse going to ARL. I have no faith in them overcoming all the hurdles you mentioned in one go.

TRENDING THREADS

-

Discussion Zen 5 Speculation (EPYC Turin and Strix Point/Granite Ridge - Ryzen 9000)

- Started by DisEnchantment

- Replies: 25K

-

Discussion Intel Meteor, Arrow, Lunar & Panther Lakes + WCL Discussion Threads

- Started by Tigerick

- Replies: 24K

-

Discussion Intel current and future Lakes & Rapids thread

- Started by TheF34RChannel

- Replies: 23K

-

-

AnandTech is part of Future plc, an international media group and leading digital publisher. Visit our corporate site.

© Future Publishing Limited Quay House, The Ambury, Bath BA1 1UA. All rights reserved. England and Wales company registration number 2008885.