N2X will allow +10% fmax over N2 according to TSMCs own slides.

14% is not a nothingburger, its actually a pretty big burger when you consider the largest gen on gen freq increase Ryzen has ever achieved was 16%, and that was only achieved once in 6 generations-- in 5950X to 7950X. The next biggest uplift, going from 12nm to 7nm, only got them 9% on paper (4.7 3950X vs 4.3 2700X). That uplift was even less in practice than on paper. That also completely ignores that the physical challenges of switching transistors at a much higher absolute frequency, at the high end of C band approaching X band.

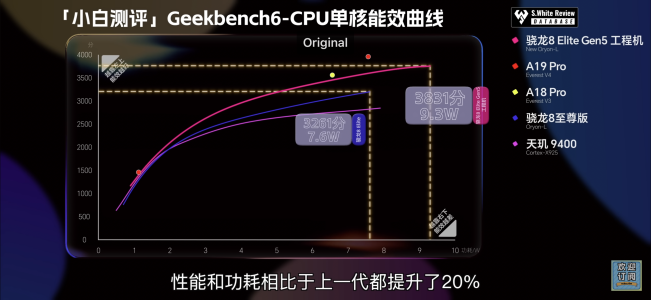

Yep and I invite people to look at Apple's frequency gains over the same timeline as Ryzen. They got MUCH more only because they were starting from a far lower frequency and - importantly - far lower power.

Newer processes don't promise 10% "fmax", they promise 10% faster transistor switching time. That is not the same thing, a lot of what would be transistor switching gains translating into frequency gains is eaten by stuff unrelated to transistor switching time such as synchronization delays and those only increase as CPUs get more complex. Also the promises of a new node "x% faster at same power or y% less power" stuff assumes the SAME design, with the same number of transistors. That's not an assumption valid in the real world, because there are always more transistors. If you get a 10% shrink and increase your transistor count by ~10% as a result that means a ~10% gain in power, so unless you want to increase your TDP by that same ~10% you must take less than x% faster switching speed.

Because Apple has been coming from a lower power world they've had more room to accept TDP increases. They've had reason to since their cores are now used in PCs instead of only phones. They've moderated that hit somewhat via the lower frequencies in phones but it is still showing up with higher TDPs in their iPhone SoCs ever since the A14 generation which was when M1 appeared. By contrast, AMD/Intel have been bumping up against reasonable TDP limits for quite a while, so they have less room to increase their TDP by the same percentage as the increase in transistor count. Apple will eventually bump up against the same limits and be restricted to the same frequency gains as AMD/Intel - they'll settle at a lower frequency range than AMD/Intel because despite their TDP increases they still place a much higher value on efficiency than the x86 world.