40% Fmax was only possible cause they had room to spare not entirely due to nodeOh noes they're all max Vt's with 3-2 finpop for Apple, even.

It's a very consistent crankage, amounted to about 40% fmax M1 -> M4 with a single full node.

-

We’re currently investigating an issue related to the forum theme and styling that is impacting page layout and visual formatting. The problem has been identified, and we are actively working on a resolution. There is no impact to user data or functionality, this is strictly a front-end display issue. We’ll post an update once the fix has been deployed. Thanks for your patience while we get this sorted.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Question Zen 6 Speculation Thread

Page 305 - Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.

adroc_thurston

Diamond Member

Not really, they were already at zoom Vt's.40% Fmax was only possible cause they had room to spare not entirely due to node

Rest was organic node CAGR, perf cells and 3-2 finpop.

Guess what? AMD can and will use all three to do just the same!

Josh128

Banned

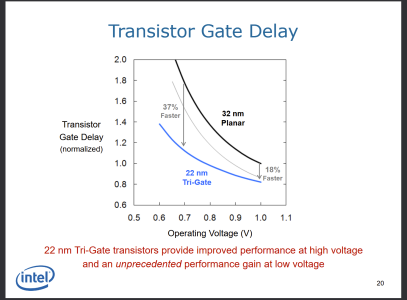

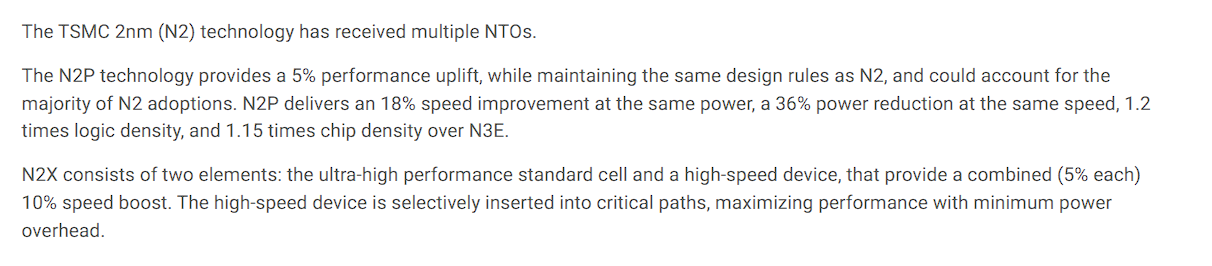

N2X will allow +10% fmax over N2 according to TSMCs own slides.N2X is maybe 2 bins of speed if you're lucky.

N3X was 1.

6.5 is a 14% fmax bump. That's nothingburger.

QC got 19% off a single shrink and a wee bit of Vmax cranking.

Apple got 31% doing just the same.

14% is not a nothingburger, its actually a pretty big burger when you consider the largest gen on gen freq increase Ryzen has ever achieved was 16%, and that was only achieved once in 6 generations-- in 5950X to 7950X. The next biggest uplift, going from 12nm to 7nm, only got them 9% on paper (4.7 3950X vs 4.3 2700X). That uplift was even less in practice than on paper. That also completely ignores that the physical challenges of switching transistors at a much higher absolute frequency, at the high end of C band approaching X band.

Last edited:

adroc_thurston

Diamond Member

It's an overdrive option and it's fake.N2X will allow +10% fmax over N2 according to TSMCs own slides.

You get 2 bins of speed. N3X is one bin of speed. Pretty simple on average.

Wordswords, Zen4 was 13% off a single shrink. They didn't even touch the perf options.14% is a pretty big burger when you consider the largest gen on gen freq increase Ryzen has ever achieved was 16%, and that was only achieved once. Going from 12nm to 7nm only got them 9% on paper (4.7 3950X vs 4.3 2700X). That uplift was even less in practice than on paper.

Josh128

Banned

And? Zen 2 was 9% off of a double shrink.It's an overdrive option and it's fake.

You get 2 bins of speed. N3X is one bin of speed. Pretty simple on average.

Wordswords, Zen4 was 13% off a single shrink. They didn't even touch the perf options.

N2X is not fake, its a very specific technology-- and the fact that its not available until '27 supports that.

adroc_thurston

Diamond Member

a) single shrink (N10 was a meme halfnode)And? Zen 2 was 9% off of a double shrink.

b) ancient history

The 10% "perf" thing is fake (you get more like 3-5%) and in any case, none of those designations apply to N2 AMD uses.N2X is not fake, its a very specific technology-- and the fact that its not available until '27 supports that.

adroc_thurston

Diamond Member

At least we've moved from "it's N3p!!!1111" to "it won't clock" kinda schizoposting. Adorable.

I think you are very optimistic about drastically increasing clocks on x86 that we have seen hide nor hair of for over a decade. I think your optimism is cute though.6.5 is a 14% fmax bump. That's nothingburger.

QC got 19% off a single shrink and a wee bit of Vmax cranking.

Apple got 31% doing just the same.

Agree.40% Fmax was only possible cause they had room to spare not entirely due to node

... and even that is at the expense of density and/or power. Lets not forget that Zen 6 by AMD's own words is "DC First design". I suspect that Zen 6 will be optimized for power efficiency. Even on desktop we are seeing the high core count Zen 5 reach socket max as the limiting factor. Adding 50% more cores will certainly place even more focus on power efficiency.N2X will allow +10% fmax over N2 according to TSMCs own slides.

Of course, it is always possible that they make a desktop version that is designed to clock scale .... but good luck getting all 24 cores up to speed under the power limit.

What is adorable is your supreme confidence in a clock speed increase the like's of which we haven't seen in quite some time .... and at a time when improvements from node to node are drastically decreasing.At least we've moved from "it's N3p!!!1111" to "it won't clock" kinda schizoposting. Adorable.

adroc_thurston

Diamond Member

14% speed bump is the least drastic thing you can get outta full node.I think you are very optimistic about drastically increasing clocks on x86 that we have seen hide nor hair of for over a decade

But you get two. Wonderful isn't it.

Nope. But you pay more.and even that is at the expense of density and/or power

You saw 13% fmax bump 3 years ago.What is adorable is your supreme confidence in a clock speed increase the like's of which we haven't seen in quite some time

They aren't, you're getting 10-15% speed a full node from now on till the end of times.... and at a time when improvements from node to node are drastically decreasing

SRAM and analog scaling died off at least.

adroc_thurston

Diamond Member

That's the same thing.that's iso voltage not peak fmax

Vmax isn't being dialed down in any real way.

Vmax is dialed down with GAAFET as they have lower Voltage than FinFetThat's the same thing.

Vmax isn't being dialed down in any real way.

adroc_thurston

Diamond Member

Nope.Vmax is dialed down with GAAFET as they have lower Voltage than FinFet

We're still at 1.4v-ish for maximum safe operation.

N3 had 1.5V ish from what i remember or was it higher still -0.1VNope.

We're still at 1.4v-ish for maximum safe operation.

adroc_thurston

Diamond Member

AMD doesn't ship above 1.45v so it's w/ever. Zero changes on that front.N3 had 1.5V ish from what i remember still -0.1V

good for them more voltage is injurious to your productAMD doesn't ship above 1.45v so it's w/ever. Zero changes on that front.

This comment is, errr, interesting. When Apple released their latest processor with their highest clocks ever, would your reasoning have been that it's impossible because we hadn't seen it before?I think you are very optimistic about drastically increasing clocks on x86 that we have seen hide nor hair of for over a decade. I think your optimism is cute though.

Not a genuine question, of course, just highlights how absurd the reasoning in comment is...

adroc_thurston

Diamond Member

It's whatever even.When Apple released their latest processor with their highest clocks ever

QCOM ships a 5G chungus (well, 2.2mm^2 is chungus enough) on a 2-2 N3x.

Note: I am addressing x86, not apple. In specific, we are talking about Zen 6 which for all intents and purposes at the core level is only a minor change from Zen 5.This comment is, errr, interesting. When Apple released their latest processor with their highest clocks ever, would your reasoning have been that it's impossible because we hadn't seen it before?

Not a genuine question, of course, just highlights how absurd the reasoning in comment is...

Zen 5 is already power limited at max core count (not frequency limited). I have speculated that in the future, we may have 1-4 cores that are "super clock" cores designed expressly to clock to very high speeds for low thread count situations. No one is saying anything like that for Zen 6 and in fact, AMD is specifically saying Zen 6 is a "server first" design.

This leads me to believe that the double process shrink 5nm class to 2 nm class will be used primarily to boost power efficiency allowing more cores to have higher performance at the same power window vs maximum frequency designs.

I am guessing Zen 6 top bin will max out at 6.5Ghz or less based on this thought process.

adroc_thurston

Diamond Member

You do understand that perf/power relationship isn't mutually exclusivethat the double process shrink 5nm class to 2 nm class will be used primarily to boost power efficiency

ToTTenTranz

Golden Member

So ..... Really? Does everyone else here buy into this?

Actually yes.

All things point to Zen5 still being competitive with Nova Lake in single threaded performance, meaning it'll be competitive in gaming. This means AMD can afford to hold on to Zen5 another quarter or two with Nova Lake in the market, if Zen6 is late.

DrMrLordX

Lifer

Where? So then you must believe that they will get 6.4/6.5 on N2P and by extension over 7GHz (+10% fmax) when they go with N2X? I think its much more likely that the 6.5 GHz rumors are rooted in the idea that N2X will make that possible.

6.5 GHz on N2P is probably doable assuming that's AMD's target. Not sure I "expect" 7 GHz at any point, and I don't know why they'd use N2X in particular? They're probably going to use DTCO w/N2P for the life of Zen6 and move on to A14 from there.

Absolutely, especially when transients seem to be so deadly nowadays.good for them more voltage is injurious to your product

Last edited:

Fjodor2001

Diamond Member

You mean until NVL-S with bLLC?Also AMD is its own competitor till Intel can match X3D in DIY.

DrMrLordX

Lifer

That seems rather optimistic.You mean until NVL-S with bLLC?

TRENDING THREADS

-

Discussion Zen 5 Speculation (EPYC Turin and Strix Point/Granite Ridge - Ryzen 9000)

- Started by DisEnchantment

- Replies: 25K

-

Discussion Intel Meteor, Arrow, Lunar & Panther Lakes + WCL Discussion Threads

- Started by Tigerick

- Replies: 25K

-

Discussion Intel current and future Lakes & Rapids thread

- Started by TheF34RChannel

- Replies: 24K

-

-