adroc_thurston

Diamond Member

It's still 48 cores.it shouldn't need a high power limit

It's still 48 cores.it shouldn't need a high power limit

Well, it differs quite a bit per CPU. Check out e.g. 9950X vs 7950X in the graph. At 200W the 9950X has about 10% higher perf than 7950X, but at 120W they are at the same perf.Probably. Pretty much every v/f curve looks like that.

Not in the way that matters. Every part shipped since the power limit stupidity (which started with Rocket Lake) can be power limited and give up a fraction of its performance. Zen 5 is actually "bad" in that respect for Cinememe. But like every dual CCD Zen before it, Zen 6 will also have eco mode.Well, it differs quite a bit per CPU. Check out e.g. 9950X vs 7950X in the graph. At 200W the 9950X has about 10% higher perf than 7950X, but at 120W they are at the same perf.

The point is that it differs per CPU how much lower perf you'll get when limiting the power consumption in BIOS settings. And certainly in a way that matters. E.g. for 9950X vs 7950X, the former drops 20% performance while the latter only drops 10%, when going from 200W to 120W. So percentage-wise 9950X drops perf twice as much as 7950X.Not in the way that matters. Every part shipped since the power limit stupidity (which started with Rocket Lake) can be power limited and give up a fraction of its performance. Zen 5 is actually "bad" in that respect for Cinememe. But like every dual CCD Zen before it, Zen 6 will also have eco mode.

Conversely, why do you think Zen 6 would be different here?

That's specific. Something we won't know until it is out. And as usual for Zen it will vary by the instruction mix.How many percent MT performance drop can we expect going from 200/230W to 120/138W? 5%, 10%, 20%, 30%, or more?

Sure. I was thinking there would be someone brave enough to take a guess already now, based on process tech, arch, core count, or whatever. I mean people are brave enough to out their perf estimates in the Hulk table.That's specific. Something we won't know until it is out. And as usual for Zen it will vary by the instruction mix.

But for the general question, nothing is different. It'll ship with power limit that throws away efficiency for approximately 10% more performance.

So you agree that Zen6 will most likely win in almost all MT workloads other than cinememe/embarassingly parallel benchmarks since very few programs can actually use all the 48 cores on Nova Lake ?Outside of embarassingly parallel benchmark it would be impossible to saturate all the cores also it's PL2

6.4GHzThanks. Frequency for ST?

Based on what you wrote in the rest of that post I have more of a despise for poorly written SW. 🙂I have a new appreciation for increased ST performance. If it comes from frequency or architecture or both.

I hear you but apparently the nature of the mixdown makes MT problematic. But yeah. It's annoying. Luckily no slowdowns during the actual mixing. But mixdown is definately a time to do other things.Based on what you wrote in the rest of that post I have more of a despise for poorly written SW. 🙂

Poorly written or is it just that some problems are not parallelBased on what you wrote in the rest of that post I have more of a despise for poorly written SW

And why can’t each of those 35 steps be parallelized in this case?Poorly written or is it just that some problems are not parallel

NC (complexity) - Wikipedia

en.wikipedia.org

If the steps must be applied in order and there are 35 independent steps, how do you parallelize it?

Most probably each step itself can be. But it ends up waiting for the slowest "substep" of each step, then add synchronization time on top of that. There are truly problems which scale poorly. I'm not sure if this is one but it easily could be the outcome of having a modular plug-in architecture where each plug-in expects memory not to be modified beneath it between its own actions.And why can’t each of those 35 steps be parallelized?

The curve might look the same, but the number axis can shift gigantically.Probably. Pretty much every v/f curve looks like that.

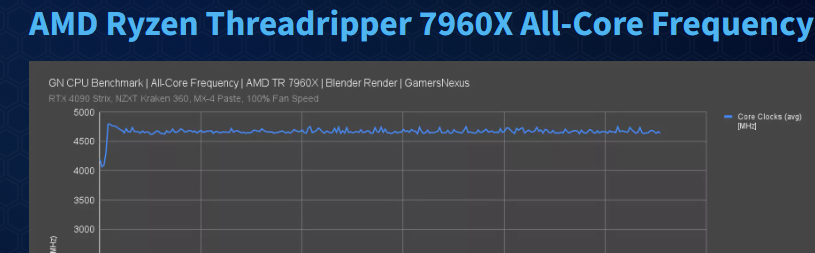

Would it? What's the IOd power for TR? and AM5 Zen 6 is TBD but most probably much less.Zen 6 24C would have to be 68% more power efficient to match this 7960X nT loaded freq with 200W

IOD alone is 100W on EPYC/TRThe curve might look the same, but the number axis can shift gigantically.

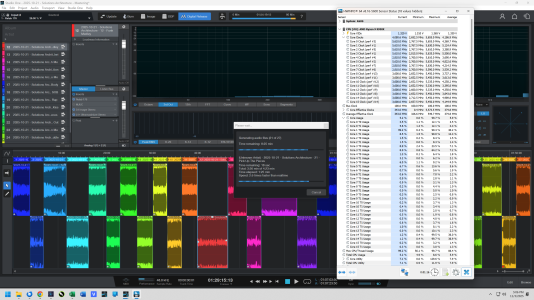

7960X, 24C, 5nm, 337W

View attachment 133137

4.650 GHz all core freq.

View attachment 133138

Even with 2nm magic, the above is why Im conservative on Zen 6 24C all core clocks, especially at 200W. Zen 6 24C would have to be 68% more power efficient to match this 7960X nT loaded freq with 200W. Im sure AMD is going to make some good strides on fixing idle /uncore power, but asking for more than 68% better power efficiency is a fairly tall order, even for a 2 node advance.

Fixing idle power is likely one of AMD's major goals with Zen 6. Even my 12 core 9900X consumes 40-50W PPT just idling on Windows desktop with HWinfo monitor running, which is not great. If they can knock that down to the sub 15W range that would be a tremendous accomplishment, but that remains to be seen. Even if they shave off 30-40W of that idle power draw, 200W PPT is still not going to be enough fuel to allow a high frequency capable 24 core to show its true power. 200W might actually be well within the sweet spot of the efficiency curve, but thats just all the more reason for them to push even more power, as you noted.Would it? What's the IOd power for TR? and AM5 Zen 6 is TBD but most probably much less.

But regardless, that Zen 6 would have to much more efficient than Zen 4 isn't surprising nor the point of what I said.

Zen 6 dual CCD part is almost guaranteed to not to ship at the best point on that curve and that's not new. That's just what they do for consumers parts that will have a high MSRP since neither competitor will step back.