Server will be first.How do you know that ? and what is the order you believe it will be ?

-

We’re currently investigating an issue related to the forum theme and styling that is impacting page layout and visual formatting. The problem has been identified, and we are actively working on a resolution. There is no impact to user data or functionality, this is strictly a front-end display issue. We’ll post an update once the fix has been deployed. Thanks for your patience while we get this sorted.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Question Zen 6 Speculation Thread

Page 102 - Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.

Of course this isn't a genuine question but do you not know what's meant by that?Color? Smell?

Kolifloro

Member

How do you know that ? and what is the order you believe it will be ?

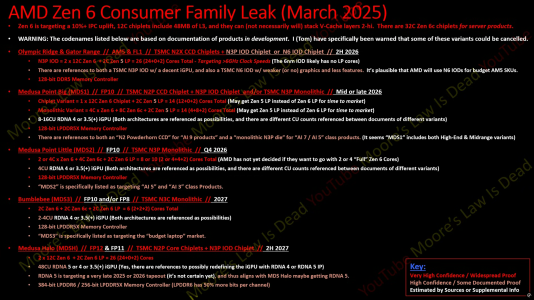

Yeah ... ... the order this time around SEEMS to be a bit different (if we take the following shot as more or less accurate ... ) ...

Ps.- It does NOT appear in the image ... but we might INFER 'Medusa Halo X3D' at around 2028 ... ... ... ... TOO DISTANT for me ...

Which is how much of the total market? Yep. Pretty thin.Of DIY? Yeah.

I would agree from an architecture point of view. I believe that Zen 6 will be strongly influenced by the need for strong DC performance.DC is number one priority

Since AMD already commands a pretty good lead over Intel in DC, they may not see the need to rush a Zen 6 DC part out right away. This may be doubly true as they will likely have a much larger CCD (~200mm2 is my guess) 32c/64t chip to produce so they will need high yields on N2 before this makes better financial sense IMO.

I think the X3D parts for Zen 6 will be the last ones on the list. Sure, they make great margins, but the number of units sold compared to other variants is pretty small.

adroc_thurston

Diamond Member

the whatThis may be doubly true as they will likely have a much larger CCD (~200mm2 is my guess) 32c/64t chip to produce so they will need high yields on N2 before this makes better financial sense IMO.

?the what

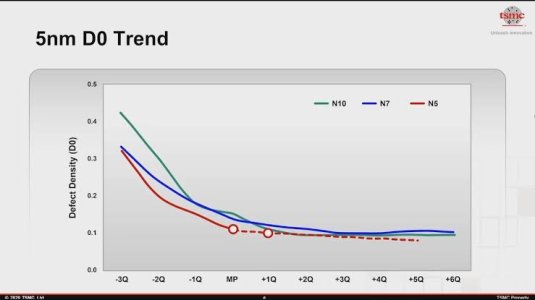

Just for reference it is between 0.2-0.1 D0 which is very healthy this is Missing N3B though and we all know why 🤣Because N2 yield is looking good, defect density D0 already <0.2:

TSMC-Fortschritte: N2 mit Defektrate wie N3, N5 und N7, großer Erfolg erwartet

Viele Gerüchte rankten zuletzt um TSMCs Ausbeute bei neuen Technologiestufen. Zum Technology Symposium 2025 gibt es Antworten.www.computerbase.de

He means the 32c server chiplet with Zen 6 Dense. But I think that should be much smaller than 200mm2.What 32c/64t part are you talking about? What in this thread, or from elsewhere, makes you think that exists?

adroc_thurston

Diamond Member

Well there's more to that thing than meets the eye.He means the 32c server chiplet with Zen 6 Dense. But I think that should be much smaller than 200mm2.

Wait a sec how are they going to cram 32 Zen 6 C core without increasing the area cause N3E to N2 is 15% and I can easily bet the core area is going to increase by a lot more than this.He means the 32c server chiplet with Zen 6 Dense. But I think that should be much smaller than 200mm2.

The 16C Zen 5 Chiplet in N3E is ~82mm2 big. Now you get N2 and a smaller PHY for the interconnect to the IOD. So it could be very well the case, that we land at ~150mm2 or so for 32C. Maybe even less.Wait a sec how are they going to cram 32 Zen 6 C core without increasing the area cause N3E to N2 is 15% and I can easily bet the core area is going to increase by a lot more than this.

i don't have doubt for that but i meant the size of the server cpu package 5c dies are compactly packedThe 16C Zen 5 Chiplet in N3E is ~82mm2 big. Now you get N2 and a smaller PHY for the interconnect to the IOD. So it could be very well the case, that we land at ~150mm2 or so for 32C. Maybe even less.

Win2012R2

Golden Member

What if all L3 will be at the bottom?So it could be very well the case, that we land at ~150mm2 or so for 32C

you mean they are using SoIC?What if all L3 will be at the bottom?

That means a much later launch, don't think they'll do thatMain lesson from Zen 5 desktop launch is that 3D version should be available straight away - even if vanilla Zen 6 beats Zen 5 3D then enough people will wait for it, AMD cracked pretty quickly and sales only took off with 9800X3D.

Win2012R2

Golden Member

Whatever they use for 3D versions - just move whole L3 cache to the bottom, that should free up space in chiplet.you mean they are using SoIC?

Why much later? Took them a few months to launch 9800X3D and zero reason they could not have done it at launch as it should have been.That means a much later launch, don't think they'll do that

My guess is that servers is #1 goal for them, hyperscalers will certainly be getting them way ahead of launch

Hyperscalers get the servers in QS stage so like 6-9 months before launchWhatever they use for 3D versions - just move whole L3 cache to the bottom, that should free up space in chiplet.

Why much later? Took them a few months to launch 9800X3D and zero reason they could not have done it at launch as it should have been.

My guess is that servers is #1 goal for them, hyperscalers will certainly be getting them way ahead of launch

Last edited:

Win2012R2

Golden Member

When do they get volume? Unlikely AMD makes one million CPUs for QSHyperscalers get the servers in QS stage so like 6-9 months before launch

After the final spec is finalized only after thatWhen do they get volume? Unlikely AMD makes one million CPUs for QS

Well, then it's smaller 😉What if all L3 will be at the bottom?

I do not think that there is too little space on the package. Yes, the chiplets are close together. But the IOD is far away. You can pack CCDs and IOD closer together.i don't have doubt for that but i meant the size of the server cpu package 5c dies are compactly packed

As an example

| Zen 5 Turin | Zen 6 |

| - 1x 400mm2 IOD - 12x 82mm2 CCD (16C) - Total = 1400mm2 | - 2x 300mm2 IOD - 8x 150mm2 CCD (32C) - Total = 1800mm2 |

So even with bigger CCDs and Dual-IOD the total Die area increases by only +25...30%. And because you pack the chiplets closer together, your "package area utilization efficiency" increases. So I do not see a problme there. It is tighter, sure. But not unrealistic.

But wasn't speculated, that Zen 6 gets a new socket with 16ch DDR and therefore a bigger socket as well?

Josh128

Banned

That would mean VERY different CCD designs for X3D vs non-X3D-- not going to happen.Whatever they use for 3D versions - just move whole L3 cache to the bottom, that should free up space in chiplet.

TRENDING THREADS

-

Discussion Zen 5 Speculation (EPYC Turin and Strix Point/Granite Ridge - Ryzen 9000)

- Started by DisEnchantment

- Replies: 25K

-

Discussion Intel Meteor, Arrow, Lunar & Panther Lakes + WCL Discussion Threads

- Started by Tigerick

- Replies: 25K

-

Discussion Intel current and future Lakes & Rapids thread

- Started by TheF34RChannel

- Replies: 24K

-

-