- Mar 3, 2017

- 1,779

- 6,798

- 136

Zen 5 architects, know. Anyway, an architecture that is new will always have some regression. It’s a matter of addressing them in the next one."But with larger test sizes, Zen 5 rapidly loses its advantage. As the test spills into L3, Zen 4 manages better instruction fetch bandwidth for both 1T and 2T modes. I’m really not sure what’s going on here."

if Chips and Cheese dont know..... who know???

With this AMD takes the crown so far.chipsandcheese

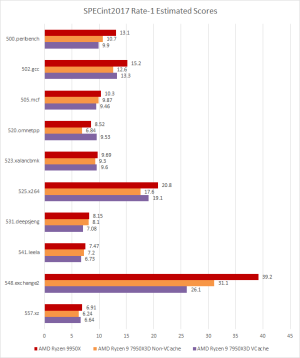

9950X spec2017

Discussing AMD’s Zen 5 at Hot Chips 2024

Hot Chips isn’t just a conference where companies give in-depth presentations on the architectures behind high performance chips.chipsandcheese.com

View attachment 107641

You are comparing apples against oranges. Two different compilers with different options enabled.With this AMD takes the crown so far.

Can Intel beat the 9950X? Intel would need 21% increase to do so.

View attachment 107643

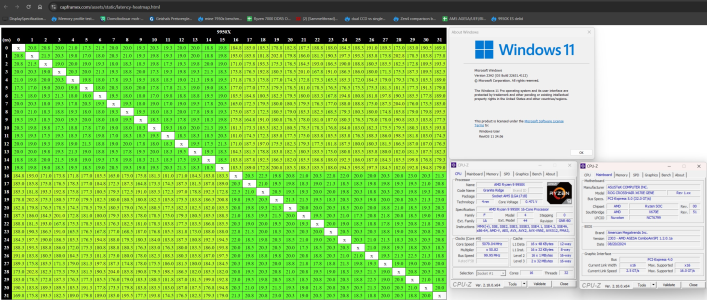

"Zen 5’s L3 cache has the same capacity and layout as Zen 4’s and Zen 3’s. However, AMD has managed to decrease L3 latency by 3.5 cycles. L3 latencies had been trending up as CPU makers add more pipeline stages to go after higher clock speeds, so it’s great to see L3 latency drop a bit in Zen 5""But with larger test sizes, Zen 5 rapidly loses its advantage. As the test spills into L3, Zen 4 manages better instruction fetch bandwidth for both 1T and 2T modes. I’m really not sure what’s going on here."

if Chips and Cheese dont know..... who know???

We'll probably find out when Zen 6 gets launched and we get the Windows update that increases Zen 5 performance.So if L3 cache latency is not the issue then what is the issue ?

I'd expect nobody, which explains why so many wrong assumptions were made about Zen 5."But with larger test sizes, Zen 5 rapidly loses its advantage. As the test spills into L3, Zen 4 manages better instruction fetch bandwidth for both 1T and 2T modes. I’m really not sure what’s going on here."

if Chips and Cheese dont know..... who know???

chipsandcheese

9950X spec2017

Discussing AMD’s Zen 5 at Hot Chips 2024

Hot Chips isn’t just a conference where companies give in-depth presentations on the architectures behind high performance chips.chipsandcheese.com

View attachment 107641

That's just a test of bandwidth. Latency decrease could have come at a sacrifice of L3 bandwidth.So if L3 cache latency is not the issue then what is the issue ?

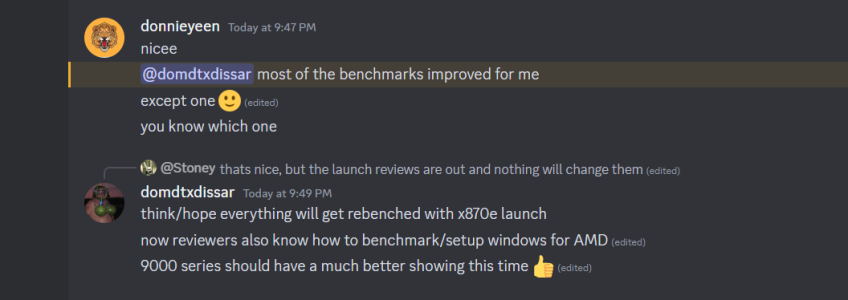

People i talk with on discord says "most benchmark improve" 😘 (even cinebench r23 ~400-600 points)It *shouldn't* impact gaming performance. Games should have stayed on one CCD, if everything else was working right.

But definitely worth testing.

That was faster than I thought. I guess I can say this now that it has happened. One of the lead architects told me that the latency regression was because they changed a bunch of tuning parameters for Zen5. It helped whatever workloads they were testing against, which is why they did it. But now that the reviews are out, they realized that the change looked really bad for synthetics. So they were going to roll it back. But they said "it would take a while" due to validation.

I honestly didn't think it would happen for at least a couple months.

If this worked reliably, we wouldn't see the games with obvious regression from 8 core to 16 core part that is fixed when disabling the second CCD.It *shouldn't* impact gaming performance. Games should have stayed on one CCD, if everything else was working right.

But definitely worth testing.

If you mean core parking then some media outlets were claiming that core parking was hurting performance rather than helping and were testing with it disabled. But since bigger publications haven't published anything about this, then I guess it can be treated as statistically insignificant. Additionally there comments that appeared after hotchips suggesting that the synthetic latency test hit some corner case and was not representative for the real latency. But since nobody tried to confirm it for now it's an interesting rumour. Especially now, that when people will retest with newer BIOS that might have tuned something inside the chip to avoid the corner case.It *shouldn't* impact gaming performance. Games should have stayed on one CCD, if everything else was working right.

But definitely worth testing.

The update is said to address performance and latency. It doesn't necessarily mean that performance increase is thanks to improved latency even if it is the easiest conclusion. I mean it would be weird for CB R23 MT to improve thanks to better interCCD latency as that would suggest tiles are dependant on each other.People i talk with on discord says "most benchmark improve" 😘 (even cinebench r23 ~400 points)

View attachment 107684

People i talk with on discord says "most benchmark improve" 😘 (even cinebench r23 ~400-600 points)

View attachment 107684

ASUS ROG Crosshair X670E Overclocking & Discussion...

I might as well start this thread now. Initially it will be sort of a placeholder as final specs are yet to be revealed. What we know is; for starters there will be two ASUS Crosshair boards, the X670E HERO and the X670E EXTREME, here is a recent stream from Asus North America presenting both...www.overclock.net

ASUS ROG Crosshair X670E Overclocking & Discussion...

I might as well start this thread now. Initially it will be sort of a placeholder as final specs are yet to be revealed. What we know is; for starters there will be two ASUS Crosshair boards, the X670E HERO and the X670E EXTREME, here is a recent stream from Asus North America presenting both...www.overclock.net

ASUS ROG Crosshair X670E Overclocking & Discussion...

I might as well start this thread now. Initially it will be sort of a placeholder as final specs are yet to be revealed. What we know is; for starters there will be two ASUS Crosshair boards, the X670E HERO and the X670E EXTREME, here is a recent stream from Asus North America presenting both...www.overclock.net

ASUS ROG Crosshair X670E Overclocking & Discussion...

I might as well start this thread now. Initially it will be sort of a placeholder as final specs are yet to be revealed. What we know is; for starters there will be two ASUS Crosshair boards, the X670E HERO and the X670E EXTREME, here is a recent stream from Asus North America presenting both...www.overclock.net

ASUS ROG Crosshair X670E Overclocking & Discussion...

I might as well start this thread now. Initially it will be sort of a placeholder as final specs are yet to be revealed. What we know is; for starters there will be two ASUS Crosshair boards, the X670E HERO and the X670E EXTREME, here is a recent stream from Asus North America presenting both...www.overclock.net

And a quote from the the author and maintainer of the y-cruncher benchmark

Indeed. Maybe they will tell us one day. Or hopefully they were able to find an acceptable middle point. But anyway people should be happy now. There is no regression on the synthetic test they couldn't even link to any other benchmark to show influence of the worse latencyThat actually sounds bad, lol. Give up performance gains on real workloads to look better in synthetics. Without any detail on what these work loads AMD was using to test against, I’m still guessing that it had more to do with power savings but we may never know the actual details.

Could you list these workloads here. I have been asking around for examples of benchmarks that could be affected by this latency regression.I find it hard to believe it was simply a matter of "tuning for real workloads at the cost of synthetics".

There are still a few very real world benchmarks that show very odd performance regressions on the 9900X and 9950X that I could only guess may have been due to the latency. It will be interesting to see if this update solves those for the expected performance scaling or not.

I'll have to look around, there were 2 or 3 MT workloads where the 9900X and 9950X failed to scale from the 9700X/9600X the same way the 7950X and 7900X did in the phoronix test suite i think?Could you list these workloads here. I have been asking around for examples of benchmarks that could be affected by this latency regression.

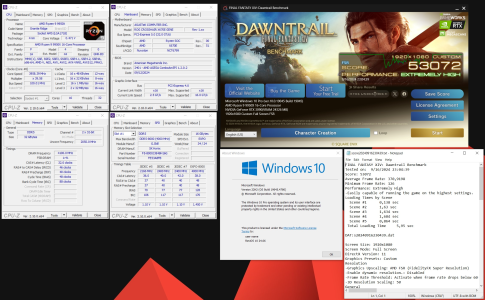

Did a little comparison myself after 3x clean installs (stock cpu clocks)

All OS's are tweaked revi with all security BS turned off

And all are running admin account

FF win11 24h2 = 49227

View attachment 107556

FF win11 23H2 (with patch) = 49565

View attachment 107557

FF win10 22H2 = 50932

View attachment 107558

Agesa 1.2.0.2Otherwise 100% same settings used for both runs, will be interesting to see how this affect the gaming performance / latency bound benchmarks

I didn't find the ones I remember in the Phoronix test suite..... There are definitely some examples that have been posted somewhere in this gargantuan thread, perhaps they are from different sources. I'll have to look through the thread when I have some more time.

I ninja edited my post.The 9950x is faster in your example.

I ninja edited my post.