- Mar 3, 2017

- 1,779

- 6,798

- 136

In their infinite wisdom, AMD marketing determined that "premium" mother board needs 28 USB ports rather than 4 memory channels.Why wouldn't anyone at AMD see an opportunity in that? Enthusiasts already pay quite a bit for the AM5 flagship CPU/mobo combo so they may not mind paying a bit more for a higher end chipset with quad channel RAM. AMD can keep 6,8 and 12 channel RAM for workstation and servers.

In their infinite wisdom, AMD marketing determined that "premium" mother board needs 28 USB ports rather than 4 memory channels.

Well if that is the cadence they hold to, it would not be surprising to see an 8+16 SKU as soon as that roadmap aligns. I think that's likely to become AMD's standard high end offering moving forward.It is not clear how it translates to desktop release schedule, but it seems that the dense CCD is not going to be lagging behind regular CCDs by very long.

It's sandwiched between the volumes of mainstream (2ch) client and lower end server (Sienna, 6ch). That's a very narrow product range.Volume could increase depending on how tangible the gains are.

Well if that is the cadence they hold to, it would not be surprising to see an 8+16 SKU as soon as that roadmap aligns. I think that's likely to become AMD's standard high end offering moving forward.

Yeah, I think that's where their vision is heading. Just need to fix most of the clock speed regression with v-cache, and then there really wouldn't be any downside vs 8+8.8 core CCD with V-cache + 16 core CCD without could be a possible top end SKU.

It seems AMD needs to overcome the challenges of dissipating the heat from the CPU better. In general CCDs and even more in CCDs with V-Cache.Yeah, I think that's where their vision is heading. Just need to fix most of the clock speed regression with v-cache, and then there really wouldn't be any downside vs 8+8.

8 core CCD with V-cache + 16 core CCD without could be a possible top end SKU.

Yeah, I think that's where their vision is heading. Just need to fix most of the clock speed regression with v-cache, and then there really wouldn't be any downside vs 8+8.

How do you feel about hybrid CPU architectures? Does it make sense to bring the Zen 4c core to desktop?

I know that Mark Papermaster talked a lot of about different core types coming into our portfolio. I guess what I would say is that as we've looked at different core types there's probably two things that are overarching factors that we think about in terms of how they fit into the portfolio. One is the notion that P-Cores and E-Cores that the competition uses is not the approach that we plan on taking at all. Because I think the reality is that when you get to the point of having core types with different ISA capabilities or IPC or things like that, it makes it very complicated to ensure that the right workloads are scheduled on the right cores, consistently.

You know what I think about when we think about different core targeting is more the question of "what type of environment is this particular core going into?" Is it an environment that's power constrained like a notebook, or is it a power-unconstrained environment like a desktop. I think that those factors are going to drive first-and-foremost how we use different core types in our roadmap in the future and I think the benefits that you see of the cloud-optimized c-core that we've talked about is in the past is something that has a significant benefit in performance per watt that fits better in a power-constrained environment. Does that make its way into a desktop processor where you're power-unconstrained, I think that's a harder argument to make. We're constantly looking at different core types, how they might fit into our architectures in the future, but I think there's some more obvious places where different core types come in and bring an advantage much more quickly than in the desktop space.

To be clear, the cost to implement 28 USB ports is minimal compared to the cost of implementing 4 memory channels with DIMMs.In their infinite wisdom, AMD marketing determined that "premium" mother board needs 28 USB ports rather than 4 memory channels.

mlid needs to touch some grass.Just FYI, MLID showed some road map where Turin Dense came ahead of regular Turin.

It is not clear how it translates to desktop release schedule, but it seems that the dense CCD is not going to be lagging behind regular CCDs by very long.

May be something on am6 with zen 6.It would be a large platform investment for a very small volume. Socket and mobo pricing is extremely sensitive to volume. And of course, you'd need a 4ch die...

They'll figure it out eventually. Thermal density is definitely a big problem, especially on newer nodes, but that's the kind of raw engineering problem that engineers love. Maybe they'll flip the stacking or something else, but I doubt V-cache will always come with such a penalty.It seems AMD needs to overcome the challenges of dissipating the heat from the CPU better. In general CCDs and even more in CCDs with V-Cache.

Eh, he kinda sidesteps it a little. And the raw technical merit of such a product is very clear. It's not going to happen for the Zen 4 gen, but Zen 5, Zen 6? I think that interview will not age particularly well, and is more targeted in the "selling the products we have today" sense.Not according to a recent TPU interview with David McAfee

They'll figure it out eventually. Thermal density is definitely a big problem, especially on newer nodes, but that's the kind of raw engineering problem that engineers love. Maybe they'll flip the stacking or something else, but I doubt V-cache will always come with such a penalty.

Eh, he kinda sidesteps it a little. And the raw technical merit of such a product is very clear. It's not going to happen for the Zen 4 gen, but Zen 5, Zen 6? I think that interview will not age particularly well, and is more targeted in the "selling the products we have today" sense.

???????????????????????????????????????????????????????????????????????????????????????May be something on am6 with zen 6.

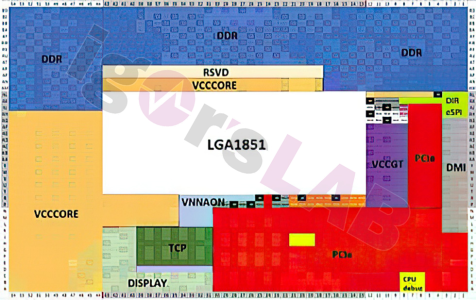

I assume Zen 6 will reuse the AM5 socket. But even if they don't, they're not going to move the mainstream off 2ch for cost reasons, nor provision that many extra pins in the socket to support both. Just to steal a pinout from Igor's ARL leak, look how many pins even 2ch takes.???????????????????????????????????????????????????????????????????????????????????????

this is all true and I agree with you with the grand exception of zen 6 being on am5. why i say this? amd is bound to take one big step and mess it all up. by then intel will e on their 2nd new ceo after pat, this ceo being a tuna fish or octopus,I assume Zen 6 will reuse the AM5 socket. But even if they don't, they're not going to move the mainstream off 2ch for cost reasons, nor provision that many extra pins in the socket to support both. Just to steal a pinout from Igor's ARL leak, look how many pins even 2ch takes.

View attachment 83277

I think, by what he says, it *won't* be Zen5. Obviously, AMD didn't do it with Zen4 - so he's not talking about that. The point of 'E' cores is Area optimized cores vs performance optimized cores. Personally, I don't see the need for this on the desktop. The current CCD-IOD system offers the flexibility AMD needs for Desktop parts. # of active cores and frequency/voltage/power limits can be set by OEM in the BIOS to get the product that they need for desktop. Mobile is a different story. Servers may be a different story - depending on what customers want (AMD could very easily provide some selective CPUs with a mix of CCDs with performance and high density cores on the same package). I don't see the benefit of having one HP CCD and one HD CCD on the desktop. IMHO.Eh, he kinda sidesteps it a little. And the raw technical merit of such a product is very clear. It's not going to happen for the Zen 4 gen, but Zen 5, Zen 6? I think that interview will not age particularly well, and is more targeted in the "selling the products we have today" sense.

There are 2 ways to interpret it - that hybrid means different instructions sets or different types of cores.Not according to a recent TPU interview with David McAfee

TPU Interviews AMD Vice President: Ryzen AI, X3D, Zen 4 Future Strategy and More

In this exclusive interview, we talk to the AMD Vice President who's responsible for AMD processors, both on desktop and mobile. Of course we had to ask about AI, but we also learned more about AM5 APUs, core counts, chiplets, Hybrid Architectures, Zen 5 and Intel's x86s proposal.www.techpowerup.com

He does say no to different ISAs or different IPCs. So, again, I’m confident that it’s a no for Zen5 and likely no for Zen6. But, as always, we shall see. All bets are off for AM6.There are 2 ways to interpret it - that hybrid means different instructions sets or different types of cores.

AMD is not going to pair CPUs that differ in the instructions they support. We will see about the other part / other interpretation.

Disclosure: I have you on blocked (so your posts aren't shown unless I am suckered into clicking the show hidden button) because you at one point posted a ton of nonsense, but occasionally something somewhat intelligent wanders from your keyboard to this forum, and I usually find out by others NOT ignoring you..so here we go:Considering where things stand:

- AM5 is dual channel

- Sienna platform is (likely) 6 memory channels

- Strix Halo is 4 internal memory channels

The chances of AMD releasing 4 memory channel socket are near zero.

What could be interesting, if Strix Halo can fit into AM5 socket, would be to have 4 internal memory channels and 2 external.

I would like to think most of us are mature enough not to accuse anyone else being a fanboy. I don't think I have ever seen anyone accuse another person on here of being a fanboy or shill unless it was clear they were were here just to cause trouble as a new account....oh and in case some new person to this forum thinks I'm an Intel fan? Look at my post history. Also please note that my household consists of 7 AMD machines and zero Intel machines (fun fact: I also have 3 RISC-V machines and 7 non-mobile ARM machines...and a bunch of Apple products that aren't listed here)

I'd don't know if we ever got updates or rebukes on these rumours since but rumours were that the new Threadripper platforms would be 8 ch (Pro, then likely based on Genoa) and 4 ch (non-Pro, then likely based on Sienna).Considering where things stand:

- AM5 is dual channel

- Sienna platform is (likely) 6 memory channels

- Strix Halo is 4 internal memory channels

The chances of AMD releasing 4 memory channel socket are near zero.

A 12-core AMD Ryzen 8050 Zen5 "Strix Point" APU has been spotted - VideoCardz.com

The first sign of AMD Ryzen 8050 It is alleged that AMD’s first Strix Point processor has now been spotted over at MilkyWay@Home website. The distributed computing platform, such as MilkyWay@Home, has become a preferred tool for AMD engineers to test unreleased hardware quickly. This approach...videocardz.com

I wonder if it occurred to the VideoCardz guy that the chip might be 12 “Zen 5” cores.

A bit of a ramble:

A lot of people are speculating that AMD will go hybrid on Zen 5, but IIRC Zen 5 work began prior to Intel publicly announcing their efforts. I am not saying this is the case, but I feel like AMD would “play it safe” by introducing a hybrid design with an existing architecture first. I will admit, however that there are some indications that AMD is pursuing a hybrid design for at least some chips.

I guess we will find out in January.

If they go hybrid for desktop, it will be interesting to see if they stick with chiplets since having multiple core designs/configs complicates the design. They would either have to move to 2 CCDs per chiplet or come up with another approach unless they are segregating server from the rest. Any thoughts on this?

I'm more interested in the rumored 'Sarlak' variant with up to 40 RDNA3 CUs.

A 12-core AMD Ryzen 8050 Zen5 "Strix Point" APU has been spotted - VideoCardz.com

The first sign of AMD Ryzen 8050 It is alleged that AMD’s first Strix Point processor has now been spotted over at MilkyWay@Home website. The distributed computing platform, such as MilkyWay@Home, has become a preferred tool for AMD engineers to test unreleased hardware quickly. This approach...videocardz.com

I wonder if it occurred to the VideoCardz guy that the chip might be 12 “Zen 5” cores.

A bit of a ramble:

A lot of people are speculating that AMD will go hybrid on Zen 5, but IIRC Zen 5 work began prior to Intel publicly announcing their efforts. I am not saying this is the case, but I feel like AMD would “play it safe” by introducing a hybrid design with an existing architecture first. I will admit, however that there are some indications that AMD is pursuing a hybrid design for at least some chips.

I guess we will find out in January.

If they go hybrid for desktop, it will be interesting to see if they stick with chiplets since having multiple core designs/configs complicates the design. They would either have to move to 2 CCDs per chiplet or come up with another approach unless they are segregating server from the rest. Any thoughts on this?