- Mar 3, 2017

- 1,779

- 6,798

- 136

Eh, all that needs to happen is for *one* benchmark to increase by more than 30% and it's winner, winner, chicken dinner. All the leakers will simultaneously orgasm.That's setting yourself up for disappointment.

I don't expect both a 40% IPC gain (already very high) and a fMax boost in the same generation. If they manage to pull a rabbit out of a hat and complete a magic trick to do that, Zen 5 will be unobtanium.

The leaker that said 39% said it was in one specific benchmark. So ????Eh, all that needs to happen is for *one* benchmark to increase by more than 30% and it's winner, winner, chicken dinner. All the leakers will simultaneously orgasm.

There is a "pre-decode cache" which stores whether a cache line stores instructions or uops. There may be distinct pre-decode caches covering each cache level (L1I, L2, L3) or a single, global cache.Rather than dropping the evicted micro-operations, the evicted micro-operations are written to the conventional cache subsystem.

Zen 5 was sampling months ago, no way any of that is in it. Zen 6, maybe even Zen 7 is where it might be.A few months back, an AMD patent about a op-cache that could spill it's contents into the L1I made the rounds in the forums:

Method and apparatus for virtualizing the micro-op cache - https://patents.justia.com/patent/11586441

There is a "pre-decode cache" which stores whether a cache line stores instructions or uops. There may be distinct pre-decode caches covering each cache level (L1I, L2, L3) or a single, global cache.

Since instructions are usually denser than uops, the patent lists some possibilities upon eviction of uops from the uop-cache: compression of immediate values in the uop cache entry, usage of two cache lines (two ways) simultaneously or just discard the decoded uops.

When uops are evicted from the L3, the patent doesn't say whether they should be written to memory. So this is volatile and not Denver-like.

While I was looking for it, I also found this:

Processor with multiple op cache pipelines - https://patents.justia.com/patent/11907126

Basically, the op-cache would be able to retrieve uops from two different addresses on the same clock. One possibility would be to fetch the instructions up to a branch and the instructions following the target address.

AFAIK current Zens can't do this (even for branches not taken), so branches do reduce the instruction throughput out of the uop-cache. Could this be what was called Zero-Bubble Branch Predictor in the Zen5 slides?

Another interesting possibility that Zen4 can't do is to fetch uops from different threads in the same cycle. This behavior can be steered by external policies (QoS) and how full each downstream uop queue is. Could make SMT even more efficient.

So, did we get any more information about it? Maybe LLVM or Linux kernel patches with related info?

Do you guys think that any of this made it into Zen5?

You said a few months back. 2020 ? Then its a maybe on Zen 5. I will wait a few weeks to see the real info.These patents are from late 2020. Too soon?

There are patents from 2022 in Zen5. Definitely not too soon.These patents are from late 2020. Too soon?

too late for ZEN4There are patents from 2022 in Zen5. Definitely not too soon.

Yeah, not contained to desktop either.With the price cuts of zen4 processors, they are probably sure that they won't sell as well once Zen5 is launched.

Every current AMD client part will go LOD before 2026, possibly before H2 2025.With the price cuts of zen4 processors, they are probably sure that they won't sell as well once Zen5 is launched.

LOD=? in this context?Every current AMD client part will go LOD before 2026, possibly before H2 2025.

Since 12 Gen core laptops are still being sold sold I think we can find Zen 4 laptops for a foreseeable future.Yeah, not contained to desktop either.

True, I just got a MSI katana 15 with Alder Lake and a 4070 for 1100€, these machines and the Zen4 are still very capable so with the right pricing (and the fact there will be reduction of the costs of N5 and N4 processes with time, they will easily occupy the lower end/mainstream part of the market.Since 12 Gen core laptops are still being sold sold I think we can find Zen 4 laptops for a foreseeable future.

So that one person, if that's the number - will prove that he actually has an excellent source compared to the rest. The rest will still boast about getting it right because they have held 8 different positions on desktop Zen5 cpus and will claim victory - aka, that one piece of spaghetti actually did stick to the wall.The leaker that said 39% said it was in one specific benchmark. So ????

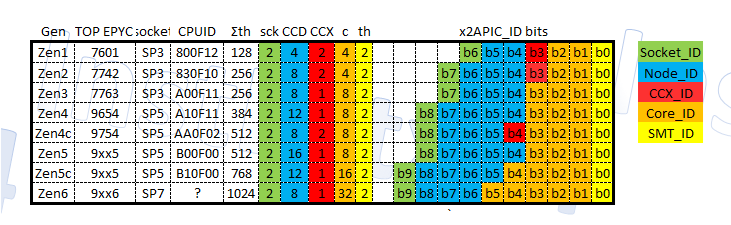

Zen5 is already old news. Leaks about Zen6 starting to appear now:

AMD Zen 6 To Feature Three CCD Configurations: 8, 16, & Up To 32 Cores, Zen 5C Packs 16 Cores In Single CCX

AMD's next-gen Zen 5 and Zen 6 core configurations have allegedly been revealed with the latter featuring up to 32 cores per CCD.wccftech.com

View attachment 99257

View attachment 99258

Why use 2x8c instead of 1x16c, for the 16c client CPU variants of Zen6?8c client, 16c server

Why use 2x8c instead of 1x16c, for the 16c client CPU variants of Zen6?

Assuming there will be 16c CCD of Zen6 available anyway, why not use them on client too? Also opens up for 2x16c on client CPUs, and 1x16c + 1x8c.

Why use 2x8c instead of 1x16c, for the 16c client CPU variants of Zen6?

Assuming there will be 16c CCD of Zen6 available anyway, why not use them on client too? Also opens up for 2x16c on client CPUs, and 1x16c + 1x8c.

Because 16c is niche.Why use 2x8c instead of 1x16c, for the 16c client CPU variants of Zen6?

I don't think the 16c CCD for Venice classic is frozen just yet.Apparently it's not just 8c/16c/32c CCDs, but 8c/16c/32c CCXs even.

No lmao.I think 3D V-Cache is everywhere