- Mar 3, 2017

- 1,777

- 6,791

- 136

What's interesting to me here is that 3D V Cache 5800 X3D is quite plentiful. And cheap, hovering around the 300 bucks mark in some stores.Well, it is not June yet, and AMD AM5 socket jumped from being behind Intel, to nearly 3x Intel. And it nearly tied AM4.

The x3d is taking the PC gaming by storm:

#1 7800x3d 1860

#2 5800x3d 1070

Zen 5 should bring that major bump. It's why I myself am hesitant purchasing into Zen 4. Intel won't catch their break for at least another 2 generations, but they release a yearly product. With some exclusions of course.Unless the Next Gen Cores are bringing a lot more uplift than the tradition we are used to.

Whenever I see how much V Cache can improve power consumption I think it must be a perfect fit for Dragon Range in laptops. The fact that V Cache is not being offered there yet tells me that while improving quantity is as of now still too little to expand beyond server and DIY desktop.I know TSMC has a new fully automated Packaging facility in Chunan inaugurated just 2Qs ago.

But does it mean that they have reached a tipping point to scale packaging for SoIC to cater to a mainstream product?

Someone else has probably pointed this out by now but this is 100% wrong right now, sorry.Zen5 (#Turin):

CPP=45nm

M2=30nm

SRAM Target = ~6 GHz at 1.2V

3nm [Zen5 was stamped in and greenlit before N3E was ever announced.]

Zen5c (#Turin-Dense):

CPP=49nm

M2=35nm

SRAM Target = ~5 GHz at 1.2V

4nm [Zen2 -> Zen3, but, Zen4c -> Zen5c // Similar architecture setup]

[Zen5] is only on 3nm. Zen5 in Turin = 3nm, Zen5 in Granite = 3nm, Zen5 in Strix = 3nm.

What's interesting to me here is that 3D V Cache 5800 X3D is quite plentiful. And cheap, hovering around the 300 bucks mark in some stores.

I know TSMC has a new fully automated Packaging facility in Chunan inaugurated just 2Qs ago.

But does it mean that they have reached a tipping point to scale packaging for SoIC to cater to a mainstream product?

On the other hand, faster GMI speeds and LLC will negate 3D V Cache benefits for gaming in the future. Unless the Next Gen Cores are bringing a lot more uplift than the tradition we are used to. Then MR DIMMs on the horizon.

Interesting times ahead.

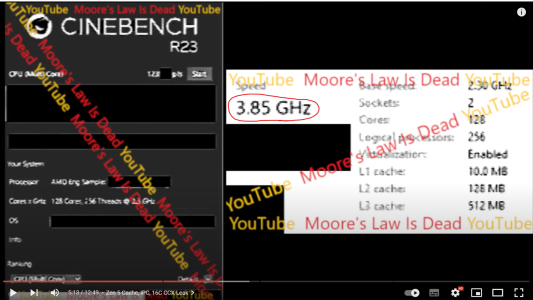

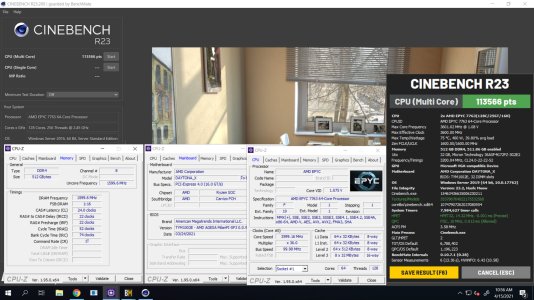

So does Tom it looks likeJim from Adore TV appears to have access to Turin Cinebench R23 scores

View attachment 79368

Without any tweaking 2S 9654 Genoa are as fast as 1P 9654 Genoa on Cinebench R23.

So 123,000 points on 128 Cores? Thats really underperforming, but its a ES so its expectedSo does Tom it looks like

View attachment 79369

It beats Genoa at the same core count, so why is it disappointing ?So 123,000 points on 128 Cores? Thats really underperforming, but its a ES so its expected

96 Core Genoa is making over 110,000 poits Zen3 EPYC gets over 113,000 points. So its not that impressive but as I mentioned, its an ESIt beats Genoa at the same core count, so why is it disappointing ?

Zen 5 in shambles, 128C Genoa > 128C Turin in CBR23. Bulldozer here we come96 Core Genoa is making over 110,000 poits and Zen2 with 128 cores(2S) get 101,000 points. So its not that impressive but as I mentioned, its an ES.

Not really, its an ES sample and to this date Sapphire Rapids can't break the 100,000 points Barrier Zen2 EPYC CPU broke long ago so Rome >>Sapphire Rapids?Zen 5 in shambles, 128C Genoa > 128C Turin in CBR23. Bulldozer here we come

I think he was joking hahaNot really, its an ES sample and to this date Sapphire Rapids can't break the 100,000 points Barrier Zen2 EPYC CPU broke long ago so Rome >>Sapphire Rapids?

I believe thats what we may be seeing here an actual 128 Core CPU but being split in two by Windows 10, like this Threadripper 3990XAs he mentioned in the video as well and was also already posted by @nicalandia : There are some real challenges regarding Windows and CBR23 when benchmarking such high thread count systems.

So it's rather difficult to take the CB scores of >64 thread systems under Windows non-Enterprise at face value.

When including that factor, the score looks pretty solid for an ES - although it still might be totally made up.

That, sadly, is the state, that Tech Journo is in.Those two? those two got access to es hardware before reputable news sites like anandtech? what is going on... Like giving a goat access to a warehouse of fancy cashmere sweaters.

why not give samples to the guy who makes 2 hour long videos and has hair reaching the ground?That, sadly, is the state, that Tech Journo is in.

Not to say that it is all their fault. People not wanting to pay for valuable content and not even being okay with disabling their ad-blockers are the root cause IMHO. </OT>

The problem is not the benchmark itself, the problem is where it originated from. I have to admit I might be a bit too critical of these few folks.As he mentioned in the video as well and was also already posted by @nicalandia : There are some real challenges regarding Windows and CBR23 when benchmarking such high thread count systems.

So it's rather difficult to take the CB scores of >64 thread systems under Windows non-Enterprise at face value.

When including that factor, the score looks pretty solid for an ES - although it still might be totally made up.

I don't think you are too critical at all. MLID is an absolute incomprehensible clown. I have no idea how people still take him seriously.The problem is not the benchmark itself, the problem is where it originated from. I have to admit I might be a bit too critical of these few folks.

But had it been someone else like Execufix for instance, I would be more willing to ponder more about it. But I am also aware about CB R23/ Windows behavior in this high thread count scenario.

Tenstorrent YT video is no longer available. Not only that slide shoddily put together, even if they have access to real data they should not have put it the way they did.