Replying to

milkegg, spam filter being wonky again.

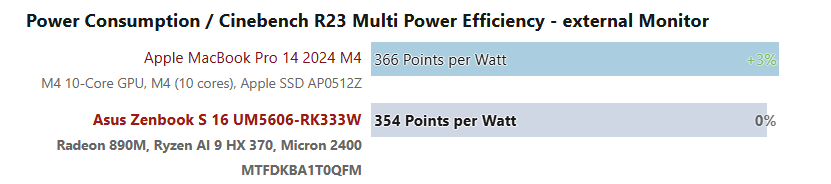

Firstly, notebookcheck measures a 7.8 watt idle power difference between the 395 and M4 pro (both with the display on), which should be a state where the cores are barely doing anything, and most of the power difference is from the SOC, memory, screen, idle tasks etc.

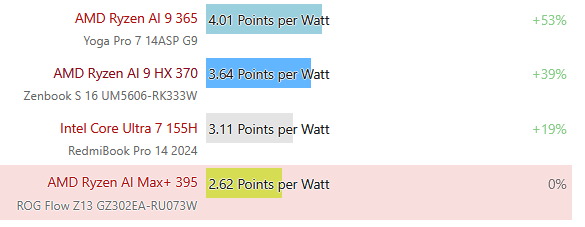

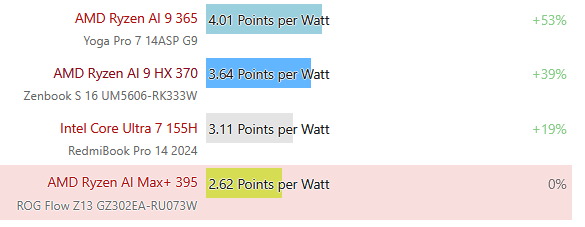

Secondly, the 395 in particular does very bad at their cinebench R24 single core efficiency test, with the 365 they tested being 53% more efficient despite having the same cores, so clearly parts other than the CPU core alone contribute a lot to the efficiency according to these tests, I don't think you can reasonably state that these tests are highly indicative of the cpu architecture efficiency.

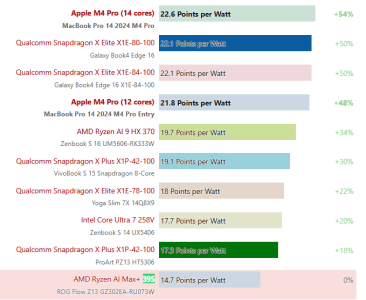

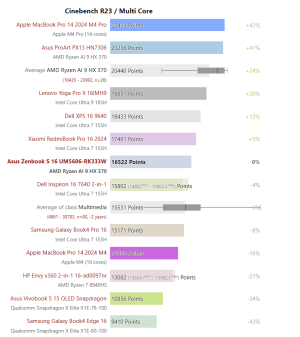

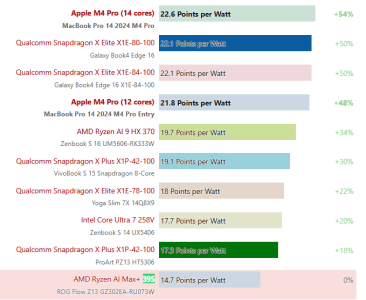

Lastly, while the 14 core M4 pro is stated to be 324% more efficient in their single core CB24 benchmark, it ends up at only 54% more efficient in the CB24 multi-core benchmark

So to me there can only be 3 things going on here:

- Apple cores get massively less efficient in multicore compared to singlecore, either due to some architectural trick that only works in singlecore scenarios or very poor multicore scaling. While I wouldn't be suprised to see some of the former, the absolute multicore performance in properly scaling benchmarks makes me believe this is not very significant.

- Amd has some magic going on that allows them very superlinear scaling (which can be easily proven to be false, they scale a little better at best, assuming equal core counts) or their cores are massively less efficient in 1t tasks (which is true, they boost further up their efficiency curve to compete in ST performance at the cost of efficiency, whereas both are at good points in their efficiency curve in MT tests).

- Other factors influence 1t power draw such as the idle power state, background work, other componennts etc. This conclusion is reinforced by point 1 and 2 also.

To me it seems obvious that based on the MT tests, where non-core power is a smaller fraction of the total power draw and where AMD is not boosting as far outside their efficiency sweet spot that the core-to-core difference in CB24 is far closer to the 54% seen in multicore (possibly lower if apple still has some uncore power advantage here, as would seem to be the case as the HX 370 with the same zen 5 cores is only 20% away from the best M4 result) than the 324% seen in single-core.

If you can rationally explain why the ST tests are representative of core efficiency and the MT tests are not I'd love to learn, but I just don't see any evidence pointing that way.