mikeymikec

Lifer

IIRC a while back someone posted a link showing how Atoms perform against mainstream processors, I'd be curious to know what the more recent generations are like against processors I know a bit better (e.g. Core i3/i5), please.

1.3x~ IPC, 2x3 Clustered Decoder, one of which can be disabled depending on the product. Configurable L2 1.5 - 4.5 MB, depending on product, the LLC can support inclusive and non-inclusive modes and it supports RDT (typically a Xeon feature). Lots of cool stuff going on here. Looks like a nice core.AnandTech Forums: Technology, Hardware, Software, and Deals

Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.www.anandtech.com

Intel Unveils the Tremont Microarchitecture: Going After ST Performance

Intel unveils the Tremont microarchitecture, its next-generation low-power small x86 core.fuse.wikichip.org

On average, Tremont has 1.3x single-thread performance on components of SPEC CPU at iso-frequency relative to Goldmont Plus.

Appears to be about/above Sandy Bridge level, though not sure the increase is strong enough for ARM Cortex-A76.

Intel’s 10nm Snow Ridge Wields Tremont Atom Cores and Mesh Architecture

An Intel-provided reference manual for Snow Ridge reveals the forthcoming 10nm networking SoC for 5G base stations is based on the Atom architecture. It also has a mesh.www.tomshardware.com

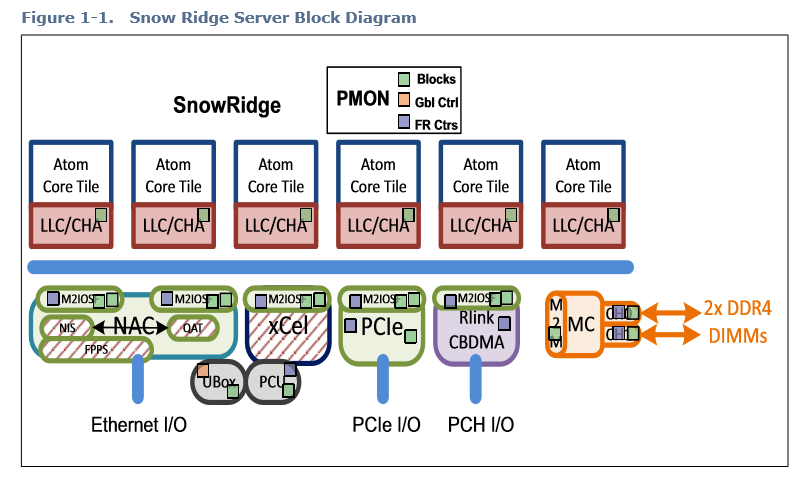

Intels Basestation chip codenamed SnowRidge appears to be using Tremont Atom cores with the Mesh Architecture seen in Skylake X/SP, Cascade Lake X/SP and Xeon Phi.

On average, Tremont has 1.3x single-thread performance on components of SPEC CPU at iso-frequency relative to Goldmont Plus.

Appears to be about/above Sandy Bridge level, though not sure the increase is strong enough for ARM Cortex-A76.

Good I am still using a Sandy Bridge i7. Now that is at 3.5 ghz and also has turbo. Goldmont Plus is turboing up to 2.5 to 2.8 ghz. Surely Tremont is going to match this 2.5 to 2.8 ghz level or surpass it. The limitation of the 8 year old sandy bridge is not the cpu but the gpu, and also other other hardware components like the ram and the ssd.

Now of course we have much faster processors than my 8 year old Sandy Bridge i7 but this is enough for casual to even serious use. People will not be complaining about the CPU they will instead be complaining the tablet / other device either uses slow MMC or does not have enough ram.

Core i5-2400 in 10 W makes for a very capable entry-level product, but whether the entry-level (ex. Celeron N4100/J4105) gets the Tremont treatment is uncertain. Likely, Intel would find selling 10 nm in networking equipment (an area which Intel has high aspirations) more worthwhile than in entry-level PCs.

Core i5-2400 in 10 W makes for a very capable entry-level product, but whether the entry-level (ex. Celeron N4100/J4105) gets the Tremont treatment is uncertain. Likely, Intel would find selling 10 nm in networking equipment (an area which Intel has high aspirations) more worthwhile than in entry-level PCs.

I've run quite a lot of tests on both Goldmont and Goldmont Plus. From my own testing, it appears Goldmont Plus is between Penryn and Nehalem in IPC. A 30% IPC uplift on top of that will result in IPC closer to Haswell.AnandTech Forums: Technology, Hardware, Software, and Deals

Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.www.anandtech.com

Intel Unveils the Tremont Microarchitecture: Going After ST Performance

Intel unveils the Tremont microarchitecture, its next-generation low-power small x86 core.fuse.wikichip.org

On average, Tremont has 1.3x single-thread performance on components of SPEC CPU at iso-frequency relative to Goldmont Plus.

Appears to be about/above Sandy Bridge level, though not sure the increase is strong enough for ARM Cortex-A76.

Looks like it will be the first Intel chip with Total Memory Encryption, an x86 extension Intel proposed back in 2017 after AMD launched Epyc with SME and SEV.AnandTech Forums: Technology, Hardware, Software, and Deals

Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.www.anandtech.com

Intel Unveils the Tremont Microarchitecture: Going After ST Performance

Intel unveils the Tremont microarchitecture, its next-generation low-power small x86 core.fuse.wikichip.org

On average, Tremont has 1.3x single-thread performance on components of SPEC CPU at iso-frequency relative to Goldmont Plus.

Appears to be about/above Sandy Bridge level, though not sure the increase is strong enough for ARM Cortex-A76.

1.3x~ IPC, 2x3 Clustered Decoder, one of which can be disabled depending on the product. Configurable L2 1.5 - 4.5 MB, depending on product, the LLC can support inclusive and non-inclusive modes and it supports RDT (typically a Xeon feature). Lots of cool stuff going on here. Looks like a nice core.

Wouldn't that just be the most Intel thing if Atom ends up setting some big new architecture shift in the future (kinda like Pentium M leading to Core 2). Almost seems like it might, and might even follow a similar setup as the Pentium M/P4, where P4 was languishing with Intel trying to push clockspeeds to keep them relevant (but that was killing their efficiency), with Atom maybe enabling Intel to pace or exceed in core counts.

I think Tremont will play an important part(emphasis on part) but it won't be the 2020's Banias.

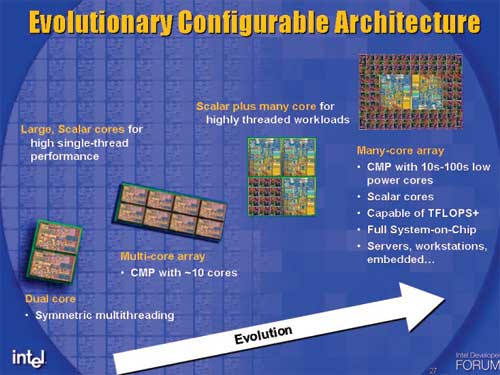

No, I believe this will be the future:

Now they finally have Lakemont and who-knows-what-else coming in the future. Tremont is a big part of that. If the Cove architectures don't deliver as well as necessary to get Intel back into performance leadership, Tremont and its successors may have to take over.

The shift to low power devices is partly why Lakefield is the future. Not just that, the level of integration will allow battery life to improve a level beyond what current Core devices can offer and be a true answer to WoA devices. You also need the big Cove cores alongside Tremont if they want to be ahead of the ARM camp, because Tremont will likely be behind A76, possibly even A75.

Let's embed that glorious slide:No, I believe this will be the future:

AnandTech Forums: Technology, Hardware, Software, and Deals

Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.www.anandtech.com

Ironic thing is Intel was the first to publicly announce it, but due to the tremendous delays to their process(and added with the stupidity of not porting IP) and anything based on those processes, they are incredibly late. If 10nm was not late, maybe we'd have seen it in 2016/2017 similar to Apple with the A10 chip.

It's amazing how they missed it when they(specifically Intel Labs lead by Justin Rattner) had the foresight to predict what's now being used in billion-plus devices today. Testament to the huge role bad management plays in everything.

I think you are mistaken believing that Sunny Cove is horribly inefficient and is a repeat of Netburst with some magic "Banias" core coming in to replace it, and that'll be Tremont.

Funny that that Intel slide pops up in an unrelated discussion about consoles.

Ironic that AMD is now (since two years) simply doing what Intel predicted in 2005 they would be doing by 2015.

But going back to Lakefield . . . Intel isn't even trying to stack Sunny Cove yet, and there does not seem to be any indication that they'll do so in a followup product. We see Rocket Lake - another monolithic design except for probably the iGPU - in 2021. We see Tiger Lake (Willow Cove) in 4c configurations, carrying on as a successor to IceLake. Unless 6c and 8c TigerLake are a thing? I haven't heard about those. We don't see 8c-16c Sunny or Willow Cove products coming up that relying on chip stacking, or anything of the sort, which is what Lakefield implies that Intel could do, if such a configuration could be made to work at all..

But will the BoM cost be acceptable to the industry / tablet mfgs / etc.? Or will only a version of the MS Surface end up using these chips, because of their (traditionally high) cost?This is their return to the Tablet market they abandoned back in 2015. But it'll be a proper one with performance no longer being anemic using the cheapest smallest cores.

But will the BoM cost be acceptable to the industry / tablet mfgs / etc.? Or will only a version of the MS Surface end up using these chips, because of their (traditionally high) cost?

ARM is everywhere, not because it's faster (although, it seems like it is, today, at the lower-end of consumer computing products), but because it was CHEAP, and continues to beso.

Edit: And what about the SOHO / SMB NAS market? Will Intel create or modify designs for their needs? I think that's a growing market. A NAS-specific SoC fabbed based on their modern Atom cores, with a RAID controller / multiple SATA ports capable of RAID 0/1/5/6, and maybe a 10GbE MAC (requiring just a PHY chip), would be nice to have, at a low cost. Certainly, it should be cheaper and lower-power, than just sticking one of their mobile Core CPUs in there, with all of the associated chipset and peripheral / I/O chips too.