So where does Tunnelborer fit in?

Simple: Tunnelborer is the 3rd variant of Bulldozer.

Complex:{{1st variation: Bulldozer -> Piledriver

2nd variation: Steamroller -> Excavator

3rd variation: Tunnelborer <== 14nm Generation Bulldozer

(Contrary to the current assumption it was not Bulldozer -> Steamroller -> Bulldozer2)

It was a 3rd iteration of Bulldozer for high performance developed between 2012 to 2014. It fell off the roadmap because it was basically building up to compete against the then Zen.

32nm -> 28nm -> 14nm

Excavator 20nm variant fell off as well, at this time rampant node switching by AMD died. Which lead to AMD cancelling off Jaguar-successors. Since, then AMD didn't have a specific low-cost part. Thus, the scraps of Tunnelborer was shifted towards ultra-low-power(2016) and exclusivity to GlobalFoundries(2018).

Main reason we haven't seen anything is GlobalFoundries has yet to solidify the research into something producible. AMD is specifically waiting for next-generation PMOS straining and first-generation NMOS strained Si. Plus, all the other research facets to improve Frequency at reduced Vdd on SOI. These features are specifically tweakable for RF variants, which is why it is needed across the board for the specific FDSOI node yet to be released. Origin wafers for 12nm RFSOI are the same as 12nm FDSOI because of strain techniques shared flow for RF and FD at GlobalFoundries. SOITEC's RFSOI/FDSOI wafers for 12nm that go to GlobalFoundries do not compete with each other.

2012-2014 => Tunnelborer - High Performance GloFo. :: 1st Bulldozer and some 2nd Steamroller team members. :: M.B. jumped ship, with chip-level multithreading being dropped, and most of were shifted to Zen. Product went into limbo.

2015 => Tunnelborer is shuffled to Low-power and renamed. :: Product was reiterated and shifted to Cat core architects

2016-2018 => The renamed core shuffled even further to Ultra-low-power. :: More aggressive re-target, returned Bobcat/Jaguar/Vulcan(Broadcom) architects<<from Broadcom CPU layoff>> and more ODC architects

goes dark

2021-Present => Core, GPU, and SoC IP is finished but the node isn't finished. :: Additional Mongoose(Samsung) <<timetable is M1-M4>> architects from SARC layoff.

There is also the more recent annoucement of the reiteration of the FDSOI roadmap:

CEA, Soitec, GlobalFoundries and STMicroelectronics working together to define technology and ecosystem roadmap PARIS, France, BERNIN, Grenoble, MALTA, N.Y., GENEVA, […]

gf.com

With tailored nodes being announced here:

Program advances long-term technology roadmap and reinforces company’s commitment to drive technology leadership of differentiated foundry solutions SAN JOSE, Calif., […]

gf.com

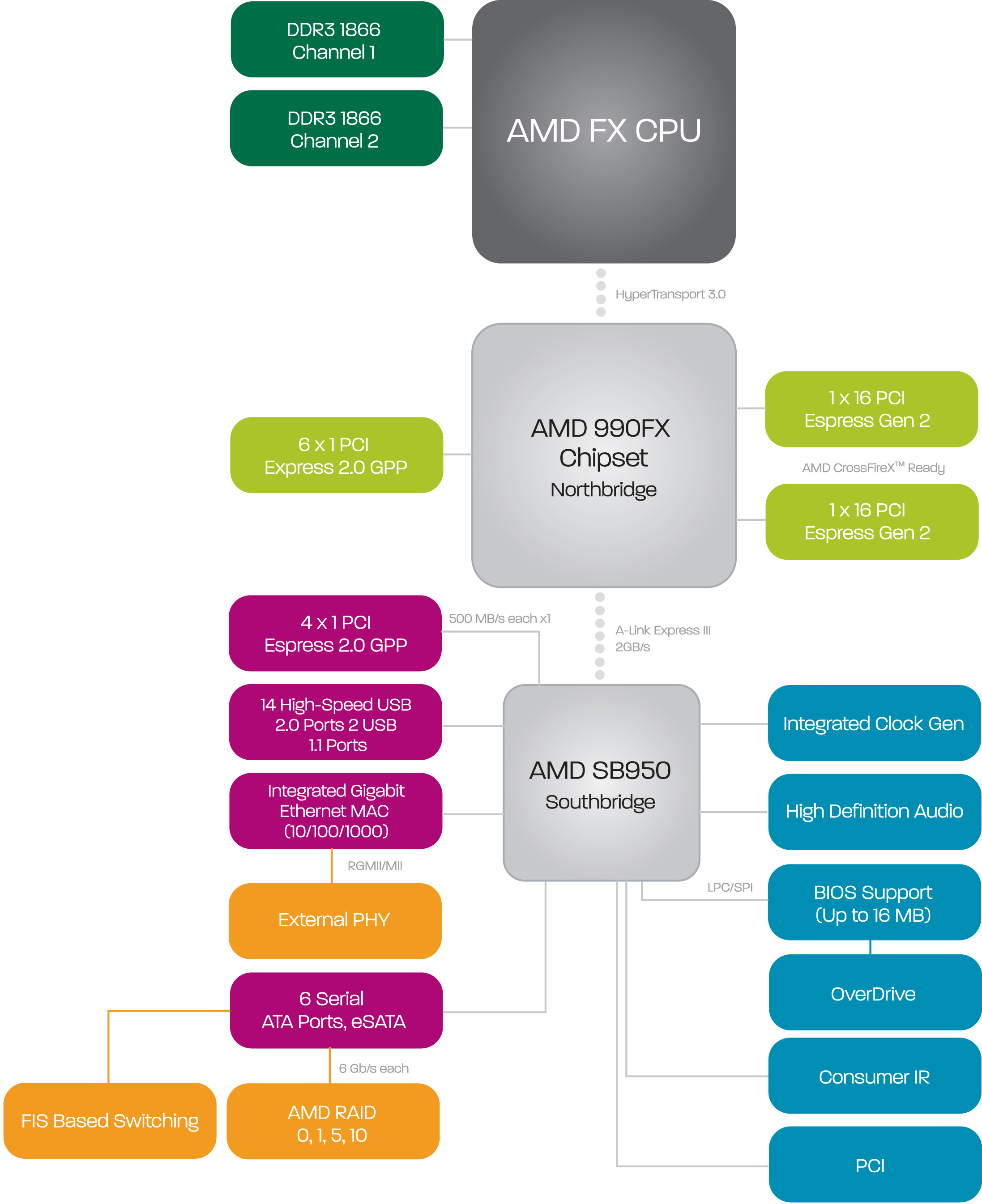

It is very likely FX will be used for TWKR/BE variants, since FDSOI has a scalable Vdd on LVT transistors. So, overclocking can be done up to >1.5V or undervolting down to <0.5V can be done.

Athlon/Ryzen/Epyc => stock voltage is in overdrive between 0.9V to 1.3V

Sempron/FX/Opteron => stock voltage is in underdrive/base between 0.4V to 0.8V

Opteron 3380/3365 1.0v stock voltage at guaranteed base frequency => New Opteron will most likely have 0.55v stock voltage at guaranteed base frequency

FX-83xx 1.3v stock voltage with base => New FX would be 0.75v stock with base

Opteron is locked in underdrive/PurePower and base/PrecisionBoost.

FX is unlocked with PrecisionBoost and overclocking potential tapping overdrive and can be tweaked for fixed underdrive via underclock/undervolting.

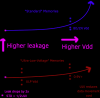

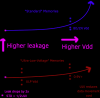

IEEE => UTBB FDSOI scaling enablers for the 10nm node (III. 10FDSOI SCALING ENABLERS)

12FDX-2019 only did these:

- Dual STI architecture as a circuit level booster

- AC performance boost by capacitance reduction

12FDX-2023 included these:

- Lg and BOX scaling (10nm Node buried oxide(15nm) is present in 22FDX+/12FDX-2019)

- Strain to boost DC FET performance

The delay is the gate length shrink and removal of added costs of sSOI NFET and SiGeOI PFET on the same wafer.

28SHP -> 22FDX-2017&12FDX-2019

0.9V -> 0.6V

Similar design or complexity => 1.8 GHz @ 0.9V on 28nm moves to => 1.8 GHz @ 0.6V on 22nm/12nm. With the changes of 12FDX for 2023 mass-prod, 1.8 GHz @ 0.6V on 12nm-2019 moves to => 2.7 GHz @ 0.6V on 12nm-2023.

First step = -70% power

Second step = +50% frequency

Should be noted the shift from HP to ULP means a huge reduction in complexity and no longer is a similar enough design. The original design was targeted at 0.9V to 1.3V like Zen, the switch to ULP meant the new target is 0.4V(0.35V) to 0.8V(0.75V). The core should have tuned ultra-low-voltage SRAMs, ROMs, PRFs, CAMs and a DTCO standard cell library for ultra-low-voltage logic. Leak across set Vdd_min to Vdd_max should be near-linear from this compared to exponential non-ULV memories.

BD -> SR -> TB => Higher Performance, which got obsoleted by Zen.

TB design re-iteration (Fam 15h = Chip-level Multithreading -> Fam Tunnelborer = Cluster-based Multithreading) -> New Ultra-low-power(Ultra-low-voltage) => Lower power, which is the successor to Dresden-originated GlobalFoundries-centric low cost platforms;

Vishera-Delhi 2018/2019 => retail up to ~155 USD (315 mm2 die)

Bristol(A12-9800, etc)/Carrizo(A8-7680, etc) 2018 => retail up to ~99 USD (245 mm2 die)

Stoney 2017/2019 => retail up to ~30 USD (125 mm2 die)

2023/2024/2025 platforms should succeed the above platforms with a new core at GloFo. The names reserved since 2016; FX <-> Opteron <-> Sempron.

May 2015 = "Zen" AMD FX CPU

February 2016 = "Zen" Opteron SoCs

Two factors lead to them switching to Ryzen and Epyc:

1. FX/Opteron were tainted with low-cost.

2. A new core was planned to fit into that low-cost, all the way back then.

The main reason the lowest bin variants of Ryzen3/Athlon parts aren't called Sempron is the same thing. Sempron is reserved for the other core on the other track.

}}

tldr of complex; Bulldozer (Desktop, HP) -> Piledriver (Desktop, HP) -> Steamroller (Mobile, HP) -> Excavator (Mobile, HP) -> Tunnelborer (Mobile-Desktop, HP, 14FF/14HP-2012 to FDSOI-2013~2014) -> New project name, similar core (Mobile, LP, FDSOI) -> Same new project name, modifiedish core (Embedded-Desktop, ULP, FDSOI)

2012~2016 leaks:

Tunnelborer: 14nm

Harvester(Forestry Excavator): Excavator on GF28FD+, rather than GF28A+ (Bristol/Stoney)

Crane(Excavator Crane): Husky-like iteration of Excavator on GF14FD+ or GF14XM, rather than GF20AN(GF20SHP/LPM).

The two above was supposed to lead towards to the new CPU core. Underlying issue occurring was SOITEC went into debt and revenue was a loss, no money to facility the GF FD ramp at the time. Hence, GF delayed for their own versions of FDSOI(derived from Albany-IBM), rather than using the licensed STM nodes. There was also issues with GlobalFoundries failing to provide shrinks themselves at this time as well. This was exacerbated by the decision of funding Malta only, which forced 2012 to 2021 to have net negative income.

Note the inversion, low-power became high performance and high performance became low-power.

Bare minimum given Cat core architects=> 2 Integer Clusters, 1 Memory Cluster, 2 Floating Point Clusters :: ILP mode: one thread across all, TLP mode: two threads across all

HP/LP (Zen) = FinFET track, and ULP (Unnamed) = FDSOI track

Example of killed but released in AMD specification: Family 15h 20h-2Fh => 10-core die "Komodo" FX with "Corona" 1090FX

Family 15h 40h-4Fh => 16-core die no die name or platform name officially announced. <-- Excavator shrinks are important for this one.

Additional 1:

So far, we have been waiting for GlobalFoundries to finish with cost-cutting efforts to facilitate the below:

Low-cost FX succeeding FX-xxxx series

Low-cost Opteron succeeding 3xxx and Xxxxx series

Low-cost Sempron succeeding A-series/E-series and consumer-orientated 3xxx(Low TDP not under Opteron)

Low-cost G-series succeeding G-series.

Prior low-income-orientated processors past Geode -> Chartered or AMD Foundry(early Sempron) =both are now> GlobalFoundries(later Sempron). New FX 2020s should be nice to compare to old FX 2010s(production dropped in 2020).

Also, a tidbit AMD SPICE'd (with GlobalFoundries' help via PPA/DTCO-engineers) something on 22nm and 12nm FDSOI in 2018. This is followed up with the January 2021-12FDX ramp up for AMD's lines for Dresden and Malta. Expanded breadth of collaboration covers 12FDX of which the new high-volume "Personal Computing" scope covers FX(unlocked) and Sempron(locked).

Additional 2:

Q3'2020 => $187 million (Ryzen salvaged 1200/1300X/2300X, RX 590/RX 640 still being run for low-price point at Asia)

Q1'2022 => $41 million (AMD following two-years after GF32/GF28 halt, significantly reduced orders of Summit/Pinnacle/Raven/Picasso/Raven2/Dali/Pollock/GFXs, focusing small supply for cIODs)

GlobalFoundries drought of PC should continue through Q2 2023, but will be solved in Q3 2023-onwards with a new FX(+Sempron) lineup replacing more expensive prior solutions.

The safest assumption in replacement of FX-8xxx/FX-6xxx/FX-4xxx/FX-9xxx CPU is that it will be dirt cheap(For AMD and end users) and not be ~315 mm2(sub-155 USD target) or ~210(sub-120 USD target) mm2. Any other details is fuzzed. As they switched away from high-performance(leaky exponential 0.9-1.3v) to ultra-low-power(linear leak increase between 0.35V to 1.5v). Which could have any amount of changes of execution units, OoO width, ULV branch predictor, FPU design, etc.

TSMC 3nm Improved High Mobilty & TSMC 2nm GAA => 2x8-pin equivalent Ultra-OC: ~$500+ CPU and ~$500+ mobo.

GlobalFoundries 12FDX => 1x8-pin (FX variant)[ignoring Sempron 1x4-pin/Mobo power variants]: ~$65+ CPU and $100+ mobo. Allows products on 12FDX to prepare end-users for products on 3nm/2nm without high-cost of failure.

EPYC(Consumer variant: Threadripper)/Ryzen/Athlon => Shrinking marketshare of total processors, increasing income and power availability(higher ASP+PPT). (staple markets: China, Japan, Korea, United States, Germany, etc) => Sell less chips at higher prices

Opteron(Consumer variant: DuoFX/QuadFX)/FX/Sempron => Growing marketshare of total processors, decreasing income and power availability(lower ASP+PPT). (staple markets: South America, Africa, Rural United States, Rural India, etc) => Sell more chips at lower prices

New Duo/Quad FX from what I can gather is a more active-cooled solution of this 4P Opteron X2150(with a non-HP reference cartridge/slot/ATX board), which falls under the compression of size of Datacenter which is Opteron however consumer-orientated Workstation-variant falls under FX:

Everything is covered in the Pervasive Computing Plan between AMD/GlobalFoundries. Again won't be talked about till AFTER the products launched:

Pervasive Datacenter is the above(<Scale-out Small Chip> Opteron).

Pervasive Personal Computing covers Gaming(FX and covers Low-cost WS, DT, Mobility), Commerical(Opteron instead of Sempron Pro), Non-gaming(Sempron)

Pervasive Embedded is the G-series.

Very cheesy: "At GF, we innovate and partner with our customers to deliver process technology solutions for

all humanity"

FX-83xx/FX-9xxx to [FX-85xx or FX-18xx or FX-x8x < FX-(generation of ZN)(clusters)(clock bin)] => significant reduction in costs and power consumption.

Timeline:

- AMD 2012 - Tunnelborer(3rd form of Bulldozer); Excavator 28BLK -> Excavator(renamed) 20BLK -> Excavator(renamed) 14FF -> Tunnelborer 14FF

- GlobalFoundries 2012 - GF licenses 28FD/14FD from STMicroelectronics.

- AMD 2013 - Shifted to FDSOI track: Excavator 28BLK -> Excavator(renamed) 28FDS -> Excavator(renamed) 14FDS -> Tunnelborer 14FDS

- GlobalFoundries 2014 - Announces collab Samsung 14nm and gets IBM property.

- GlobalFoundries starts loss spree with SOITEC leading to death of standard FDSOI to give time for SOITEC|GF

- GlobalFoundries 2015 - Announces shift from STMicroelectronics FDSOI to internal from IBM: "Advanced FDSOI"

- AMD 2015 - Cancels post-Jaguar(20BLK/14FF designs went TSMC first, then GloFo) and Excavator shrinks(FD-work as well), shifts TB architecture to new name LP design point for "Advanced FDSOI"

- GlobalFoundries 2016- "Advanced FDSOI" has thus been named "22FDX" and given a successor node "12FDX"

- AMD 2016 - new name LP architecture is shifted further down to ULP design point for "22FDX/12FDX"

- SOITEC 2017 - Turn around into profitability after PV Solar Cell disaster(also, hit SunEdison)

- GlobalFoundries 2018 - Stops funneling CapEx to FinFETs(losing money) from other projects(gaining money).

- AMD 2018 - One foot in, initial ULP IP layout/floorplan, exclusive to GloFo because of DTCO/PPA-enhancements.

- CEA-Leti 2016-2020: Strained NFET is hype! Strained 12FD wafers hype! 2020: Cheaper steps for sSOI NFET + SiGeOI PFET found!

- GlobalFoundries 2019 - 3D Logic-on-Logic development taped out

- GlobalFoundries 2020 - 12FDX is officially delayed and back in the oven at 60% done.

- GlobalFoundries 2021 - 3D Logic-on-Logic production-ready and 12FDX integration begins at both Dresden and Malta.

- AMD 2021 - Officially in 12FDX sphere with expanded(switching tracks) collaboration for 2023-2025.

- Not yet, GlobalFoundries 2022 - Starts 12FDX ramp for 2023+. Backwards compatible to initial 12FDX PDK, RTOs can go into production immediately.

Addition #3:

Reasons for Opteron/FX/Sempron:

- AMD is losing the software support to cheaper solutions by competitors: Intel-based, ARM-based, RISCV-based

- AMD is expected to lose hardware volume to cheaper solutions: higher Server/PC share is ARM-based. x86 Server/PC is -7% - YoY loss, AMD is gaining a shrinking share of x86, while ARM is growing faster. ARM is growing fast because it has a low-cost foundation of software support, that can be scaled up towards compute hardware.

Taking the data, the answer is to clearly release a cheaper solution. That is viable to low-income end users and resistant against downturns in economy/purchase habits(5~8 year upgrade cycle). Good enough at low price is the king, higher performance at higher price is the fool. The prior statement is for generalized software support, cheaper = more, expensive = less.

Strict goldilocks zone: $99 to $199 USD for system(SoC/RAM/Board) for standard {FX/Sempron market} end-user. Costs for small chip scale out for servers on older nodes haven't been an issue.

With the buffer zone going up to $299 USD, going further than that is hobby-enthusiast territory.

Primary targets:

FX => ARM-based ATX w/ wider overclocking support via increased power over SBC OC. Bigger ATX versions generally also have higher stock clocks.

Opteron => Cheaper ARM-based small chip scale-out processors. Newer ARM processors being pulled to older nodes.

Sempron => Generic Mini-Desktop/Laptop/etc mainly aimed at ~5W. Cheaper solution of ARM on older node.

G-series => Aggressively lower TDP variants of above.

Stuff that AMD can't service because of "Zen" track chasing ever expensive nodes. However, there was an ever-present window at GlobalFoundries and the window is definitely present now. With GF's operations going from first-world/high-cost markets(chasing smaller transistors) to global-world/low-cost markets(chasing larger markets => design smarter(3D-stacking, etc) not smaller(expensive scaling)).

Shortened:

- Tunnelborer started in 2012 and continued on...

- Switching to low-power occurred in 2015 and the further switch to ultra-low-power(ultra-low-voltage) occurred in 2016. With High-Perf to Ultra-low-power(ultra-low-voltage) changing general architecture details and even changing the code used for it.

- Of course, through the switching largely fell onto GlobalFoundries reduced-cost nodes. Which is followed up by the switch from revenue-orientated to volume-orientated selling of wafers. (AMD is required to buy a higher volume of wafers not a lower volume of higher priced wafers)

- With the product stack sweeping and collecting old low-cost versions of Datacenter, Personal Computing(Gaming/Commercial/Non-gaming), and Embedded.

- Which was AMD's most successful stack, ignoring that they were quickly hopping from expensive shrink to ever more expensive shrink.

- With that FX is returning as the higher TDP variant and pulling out 2P/4P variants as well for workstation (low-cost consumer scale-out).

Context to FX-8350:

- AMD has ended manufacturing capability of 32nm

- Selling a 315 mm2 with outdated power management and higher TDP at lower cost, has no innovation => no hype train

- 90/65 -nm FX -> 32 -nm FX -> 12 -nm FX

- Where the 12nm FX achieves a much smaller die(lower than 315 mm2, lower than 210 mm2, without cost-additives(FinFET/2.5D packaging(bad for low-cost)), uses lower TDP(low opt: 100W processors(module power consumption) -> 25W processors, same clocks => high opt: 100W -> 10W processors, higher clocks)

Three core is back:

TSMC Cores:

Performance => Zen-line with full FPU(4-pipe/6-pipe) (similar ex: Greyhound(Fam 10h) with 128-bit FPU)

Value => Zen-line with cut FPU(2-pipe/3-pipe) (simple way to cut leakage/power consumption) (similar ex: Lion(Fam 11h) with 64-bit FPU)

GlobalFoundries Cores:

Pervasive => Successor to Bulldozer, ULP core. ==> With the ULP core including the fix for "There are no separate single-threaded or multithreaded operation modes."

Safe to assume:

Manchester (90nm SOI)_89W/Dual-core/2 GHz -> Ontario (40nm Bulk)_18W/Dual-core/1.6 GHz

Zambezi/Vishera (32nm SOI)_125W/Quad-processor(Defined as Octo-core)/3.5 GHz -> FX ULP SoC(12nm FDSOI)_25W/Quad-processor(Defined as Octo-cluster)/3.5 GHz

The reason for clocks remaining the same is from same node lineage(32SHP => GF -> 12FDX => GF), where Bobcat went to a node lineage that supported less frequency(higher leakage at higher Vdd). Other reason for same frequency is the shift away from standard memories:

The biggest threat is Cortex-A710 on TSMC 22nm and TSMC 12nm. More scalable than any 7-class core before it, meaning any products that have a desktop variant will be overclockable. However, the nodes to worry about are UMC 22nm/12nm, [SMIC 22nm/12nm, and HLMC 22nm/12nm]-same research and development group.

- AMD leaves the low-cost room. (successful >5 mil processor per quarter sells)

- ARM-developers peeks in... It's free real estate. (extra successful >10 mil processor per quarter sells)

Thus, continued sales of the current FX-8000s is unreliable(hence, the halt of GF32/GF28) as the main competitor is smaller and cheaper. Zen is not cost-effective towards older backported ARM chips, so support for AMD chips dwindle. Emulation/translation x86 to ARM increases, which can be scaled up to newer >64-core Neoverses, thus removing one the major reasons to get EPYC over a Neoverse-variant. ARM is better for its cheaper cost, Zen is in a downward spiral of demand/reduced accessible market, which is covered up by higher average selling prices and higher performance.

$8000-$9000(peak AMD-64C CPU-only) => $6000(peak ARM-128C CPU-only)/$4000(peak ARM-80C CPU-only)

>$4500(AMD-32C workstation (full system)) => <$3600(ARM-32C workstation (full system))

$100-$600 (ARM-4C~16C Entry-workstation(OC-supported)/Entry-server/Entry-desktop(OC-supported) system cost) => *crickets*

//More focused on the higher sales of the $100-$300 range. -- Zen is low supply at TSMC for low-cost, while GlobalFoundries is sitting at high supply while not currently utilized.

FX Quad-processor $189-$155 (full die) -> Ryzen 1st through 3rd Quad-processor $129-$99 (Salvaged die) -> Ryzen/Athlon 4th Quad-processor ~$150 (Salvaged die)

Market share indicators place FX(FX-8350) as more successful than 1st through 3rd generation 1CCX disabled. In this portion, if these did become successful they are undercutting $300-$500 Average Selling Price.

Current market: $3000 (32SOI) -> $2000 (28BLK) -> $2000 (22FDX) -> $3000 (12FDX) versus 14FF/12FF $4000 to $5500.

32nm PDSOI had potential for a larger volume but most of SOI fabs were swapping to FDSOI wafers. (PDSOI decreased in availability)

Trusty calculator:

$3000 / 132(Good dies) => $22.73 ratio to $155 + Hypothetical Orig ratio to current price of wafer $245(FX-8150)

$4000(GF-current) / 264(good+defective dies) => $15.15 ratio to $130 and $100

$9000(TSMC-current) / 359(good+defective) => $25.07 ratio to $150

$3000 / 498(Good dies: Monolithic, half-die size of Summit/Pinnacle) => $6.024

Most recent FX SEP = $41.1

Original FX SEP + current wafers: $64.9

Ryzen high-end Quad-processor + current wafers: $51.7 :: MP cuts into ASP for this and the two below.

Ryzen low-end Quad-processor + current wafers: $39.8

7nm Ryzen/Athlon + current wafers: $36.04

Highest margin appears to be the ratio'd of original FX price with modern wafer prices.

With ELTS of AM4 (higher position higher price):

ELTS Zen3 (6nm for eventually 10nm DUV pricing?):

- 16-processor

- 12-processor

- 8-processor

- 6-processor

ELTS Zen2 (6nm for eventually 10nm DUV pricing?):

- 6-processor (Renoir)

- 4-processor (Renoir)

New core on ELTS-AM4

- 4-processor (New FX/Sempron)

- 3-processor (New FX/Sempron)

- 2-processor (New FX/Sempron)

AM4 LTS(support of 5 years) => 2017 to 2022

AM4 ELTS(support of 10 years) => 2017 to 2027

AM3+ FX:

New platform (lower availability)

New process generation (lower production)

Higher process cost than before (lower margin)

High initial TDP: 140W/125W/95W and general focus on higher costing motherboards.

AM4 FX under Extended portion of Long-Term-Support:

Mature platform (higher availability)

Existing process generation (higher production)

Lower process cost than before (higher margin)

Low initial TDP: 25W+10n[N=0-2] with additional PPT up to 95W (AM4 Ultra-Budget = ~$50 USD) or higher 142W (AM4 Budget: ~$75)

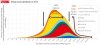

Market share :: Power consumption globally

Low-cost: ~50% :: ~60%

Mainstream-cost: ~35% :: ~15%

Enthusiast-cost: ~15% :: ~25%

Reducing low-costs global power consumption is why TDP is low. 700W CPU + 800W GPU, better hope the plebeians aren't grasping all the power.

General idea (CPU[2023] or CPU+GPU(w/ 3D memory => extends to AIB form cost-savings)[2024])

FDSOI CPU or GPU and I/O can be on the same die, but CPU and GPU can not. BEOL-optimization for best PPAC is specific to CPU-centric or GPU-centric. With this CPU+I/O can be on a single die. Rather than an I/O die with a hub config, it would be a GMI Switch Die. (GMI<->CPU links, plus snoop filter cache, etc. Virtually one-NUMA, physically many-NUMA.)

FDSOI: Same FEOL for Logic and I/O => BEOL has specific optimizations between CPU and GPU => CPU+I/O and GPU+I/O can be done with two dies with max figures of merit.

FinFETs: Seperate FEOL for Logic and I/O => BEOL is same => CPU+I/O and GPU+I/O needs four dies to max FoM.

ELTS Legacy Platforms:

AMD FX/Sempron AM4 - scale up -> AMD Ryzen/Athlon AM4

scale-out

AMD Opteron SP3 - scale up -> AMD EPYC SP3 > however I don't think SP3 was extended life:

Zen stops production sometime in 2023 and Zen2(14nm IOD) stops production sometime in 2024.