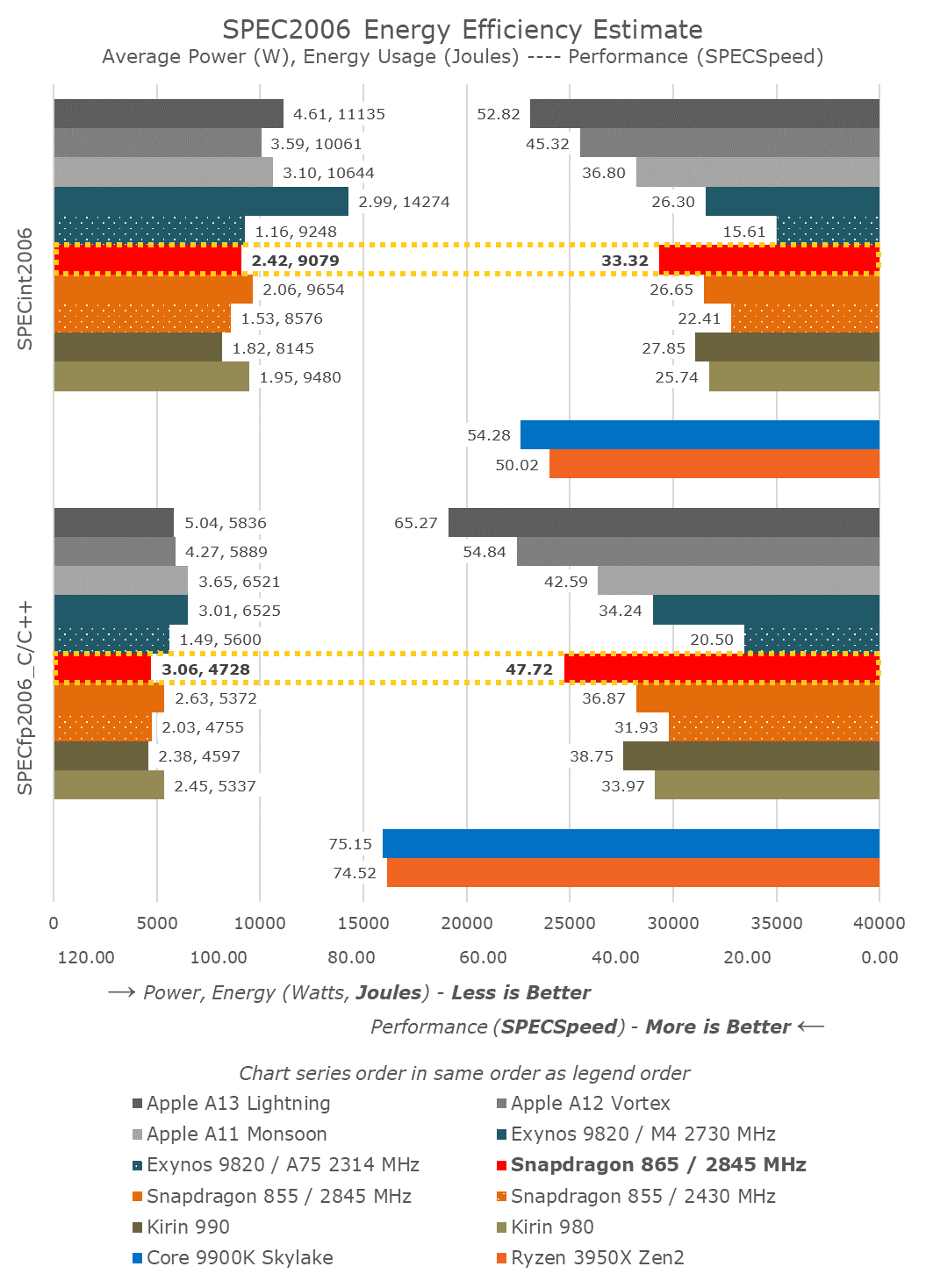

Apple's A13 is beating very fine binned Ryzen 9 3950X @ 4.7 GHz. If you would set Zen2 at clock every chip is capable of (like A13 is) then it would be somewhere around 4.2 Ghz.... and A13 would win over Zen 2 with higher margin. 64-core EPYC with TDP 280W (4.4W/core at 2.5 GHz) looks very competitive with A13 (5W/core @2.6 Ghz). Until you realize A13 has a massive +82% IPC advantage. EPYC would need more than 1000W TDP to be able to run at 4Ghz and be still slower than A13@2.6 GHz. I tell you guys Nuvia server chip with IPC like A13 would be total killer for most x86 server world today. AMD needs +25% IPC jump every year to stay competitive against Nuvia on 2024. That's why Zen3 must be something very good. Much better than leaks suggests. If +12% INT IPC gain is correct for Zen3 then AMD will fall into mediocrity again (same as K10.5/Barcelona/Thuban age).

AMD will not fall into mediocrity unless they manage to fall far behind Intel when they should be in the lead.

The ARM server/desktop market may certainly grow in the future, but it's not going to displace x86 significantly anytime soon.

Besides which, by 2024 Nuvia will have competition from ARM themselves inevitably, A78 is due in May and we will probably still see a new core every year from ARM

It's easier to just write K10 age (or Stars using the desktop codenames).

You somehow managed to use 3 different variants of codenames in differing generations of it there.

K10.5 is the second gen core, Barcelona is the first gen server SKU (Agena is the desktop variant also affected by TLB errata), Thuban is the desktop SKU for K10.6/third gen core/6 core monolithic.

I get testy about the K10 comment because I had a Phenom II X4, it was a great chip for much better value than the Intel product on the market.

Bulldozer was mediocrity, K10 was just second best of it's generation, but a good second best well worth buying at the time.

Apple ends up with the most advanced CPU core on the world with massive +82% IPC advantage over Zen 2.

The most advanced CPU core? Arguable to say the least with the likes of A64FX knocking around now with 512 bit SVE - there's more to being advanced than great scalar IPC.

Remember that for all that vaunted scalar oomph, Axx cores are currently crippled in the SIMD arena when comparing to x86 Zen and Core competitors.

Apple also lacks the software on any iOS platform that compares to x86 systems using MacOS, Windows or Linux - all that awesome IPC is as useful as a paperweight for most serious work outside the new Photoshop iOS release.