Speculation: Ryzen 4000 series/Zen 3

Page 58 - Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Olikan

Platinum Member

- Sep 23, 2011

- 2,023

- 275

- 126

That's exacly the size of Vega L1 cache...Glad to hear the rumor about Vega is likely false. Does the 16kB of L2 refer to the GPU cache (it surely must right)?

RetroZombie

Senior member

- Nov 5, 2019

- 464

- 386

- 96

I don't see any problem if it's still Vega instead of RDNA, I think Vega is actually a very good architecture and is very power efficient, for example Vega 56 mobile is 120 Watts for the all card, the Vega M GL is 65 Watts, Nvidia for example have many 120 Watts and more and just for the chip.

I think I'm the only one and maybe Moore's Law Is Dead that likes it.

I think I'm the only one and maybe Moore's Law Is Dead that likes it.

Thunder 57

Diamond Member

- Aug 19, 2007

- 4,215

- 7,002

- 136

AMD Mark Papermaster actually didn't reject SMT4 for any upcoming product. This is a bit strange because he could do that and stop all speculations about SMT4 (unhelthy for stock market) and just confirm SMT2 from that leaked presentation. However he did not. Maybe he couldn't do that because Zen3 will support both SMT2 and SMT4.

AMD CTO Mark Papermaster: More Cores Coming in the 'Era of a Slowed Moore's Law'

Get ready for more coreswww.tomshardware.com

And if he had flat out denied it, you would be saying it's because its some big AMD secret, just like the AMD employee who made that slide did.

Speculation is fun. But when all the evidence points one way, you might want to think about changing your mind.

Last edited:

ClockHound

Golden Member

- Nov 27, 2007

- 1,111

- 219

- 106

And if he had flat out denied it, you would be saying it's because its some big AMD secret, just like the AMD employee who made that slide did.

Speculation is fun. But when all the evidence points one way, you might want to think about changing your mind.

Evidence has been recently proven to be ineffective for mind changing. Here in this forum and farther out.

Since it's speculation until the final product evidence is released and changes no minds, I'm going on the speculative record with SMT3. The boring power of 2 dominance in this industry needs the odd shakeup. And Zen 3 is perfectly named for the task.

Panino Manino

Golden Member

- Jan 28, 2017

- 1,151

- 1,395

- 136

In situations like this you DO NOT confirm ANYTHING.AMD Mark Papermaster actually didn't reject SMT4 for any upcoming product. This is a bit strange because he could do that and stop all speculations about SMT4 (unhelthy for stock market) and just confirm SMT2 from that leaked presentation. However he did not. Maybe he couldn't do that because Zen3 will support both SMT2 and SMT4.

Why would anyone do this, so ahead of time and "help" his competition?

He just used his liberty to muse about the state of the market and the many possibilities available.

Thunder 57

Diamond Member

- Aug 19, 2007

- 4,215

- 7,002

- 136

Speculation aside, what the heck is the fascination with SMT4? Because it really hasn't been done before (or at all in x86-land)? If AMD saw a reason for it, I'm sure they'd be working on it. With the massive amount of real cores available these days, I really question how much doubling threads would help outside of very specific use cases.

AMD Mark Papermaster actually didn't reject SMT4 for any upcoming product. This is a bit strange because he could do that and stop all speculations about SMT4 (unhelthy for stock market) and just confirm SMT2 from that leaked presentation. However he did not. Maybe he couldn't do that because Zen3 will support both SMT2 and SMT4.

AMD CTO Mark Papermaster: More Cores Coming in the 'Era of a Slowed Moore's Law'

Get ready for more coreswww.tomshardware.com

And if he had flat out denied it, you would be saying it's because its some big AMD secret, just like the AMD employee who made that slide did.

Speculation is fun. But when all the evidence points one way, you might want to think about changing your mind.

Papermaster was fairly ambiguous on the subject touching on both hardware and software viability of the concept, though he seemed to be leaning towards it being of limited application at the current time in the software market.In situations like this you DO NOT confirm ANYTHING.

Why would anyone do this, so ahead of time and "help" his competition?

He just used his liberty to muse about the state of the market and the many possibilities available.

The entire talk was geared towards cores more than threads, as is Zen itself so far.

Even with just SMT4, they've already reached a thread count per socket that is 32x that of the PD CMT based Vishera's in early 2017, even without SMT4 the thread count will increase anyway, at worst every 2 years by current Epyc generation cadence.

What's more is AMD is already giving the customers what they want, admitted by Intel's own employees recently - I don't think they are in danger of new customers straying from Epyc any time soon.

RetroZombie

Senior member

- Nov 5, 2019

- 464

- 386

- 96

Intel already have done it in 2016 if you include:Speculation aside, what the heck is the fascination with SMT4? Because it really hasn't been done before (or at all in x86-land)?

https://en.wikipedia.org/wiki/Xeon_Phi

Thunder 57

Diamond Member

- Aug 19, 2007

- 4,215

- 7,002

- 136

Intel already have done it in 2016 if you include:

https://en.wikipedia.org/wiki/Xeon_Phi

Interesting, did not know that. Kind of seems to indicate I may be right when I said above about it only being useful in very specific use cases.

Thunder 57

Diamond Member

- Aug 19, 2007

- 4,215

- 7,002

- 136

Something something broken clock I guess.

Some people don't watch long YT videos especially when they don't know what they're looking for. Especially when there is a print version that is much easier to navigate.

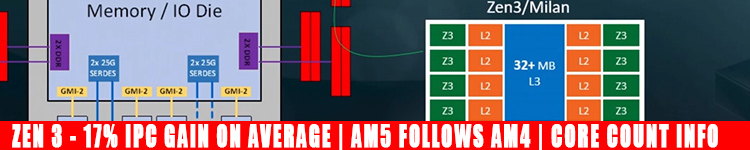

AMD Zen 3 - More Info on IPC & Clock Speeds & AM5 Follows AM4 | EXCLUSIVE

AMD's Zen 3 processors will be pretty special, because not only will be the final Zen architecture on their respective sockets and platforms but also becau

www.redgamingtech.com

Also, I don't think anyone ruled out SMT4 forever, but certainly won't be in Zen 3. That's exactly what this guys sources said. No SMT4 in Zen 3.

Thunder 57

Diamond Member

- Aug 19, 2007

- 4,215

- 7,002

- 136

Yep. 17% IPC overall and no SMT4 for Zen 3. Also no real clock bumps for Ryzen 4000 series.

Hence the broken clock comment. The guy finally gets to get something that's not the Radeon VII right.

Good on him.

I didn't know what you meant about the broken clock thing, so I'm sure there were others. The 17% IPC may be a bit high, but would be great if true.

IntelUser2000

Elite Member

- Oct 14, 2003

- 8,686

- 3,787

- 136

Intel already have done it in 2016 if you include:

https://en.wikipedia.org/wiki/Xeon_Phi

You can't use Xeon Phi cores as a comparison, because it was aiming for the market that was better for GPUs. GPUs use many threads to cover high latency scenarios. Also note that the original Xeon Phi was based on Larrabee, which is an x86 core based GPU.

To be fair that guy has a very strange way of talking - like a British English accent but extremely deep with terrible pronunciation of basically everything.Some people don't watch long YT videos especially when they don't know what they're looking for. Especially when there is a print version that is much easier to navigate.

AMD Zen 3 - More Info on IPC & Clock Speeds & AM5 Follows AM4 | EXCLUSIVE

AMD's Zen 3 processors will be pretty special, because not only will be the final Zen architecture on their respective sockets and platforms but also becauwww.redgamingtech.com

Also, I don't think anyone ruled out SMT4 forever, but certainly won't be in Zen 3. That's exactly what this guys sources said. No SMT4 in Zen 3.

It's so bad that at points I'm fairly sure he's trolling the audience for kicks or channel 'uniqueness' factor.

Panino Manino

Golden Member

- Jan 28, 2017

- 1,151

- 1,395

- 136

A bit radom, but... many people used to criticize AdoredTV for his speculations, but since "his rise" I noticed the birth of a few new channels that are just about rumors and hype. All milking this current AMD moment.

And I don't see people bashing them from riding in the wave AdoredTV created.

And I don't see people bashing them from riding in the wave AdoredTV created.

IntelUser2000

Elite Member

- Oct 14, 2003

- 8,686

- 3,787

- 136

A bit radom, but... many people used to criticize AdoredTV for his speculations, but since "his rise" I noticed the birth of a few new channels that are just about rumors and hype. All milking this current AMD moment.

And I don't see people bashing them from riding in the wave AdoredTV created.

That describes 90% of youtube.

Have you seen videos on youtube where it has a very fancy title or the thumbnail has a big bright colored arrow pointing at something ambiguous?

Extremely click-baity and misleading but based on viewer count it at least attracts people to click on it.

Most of those videos talking about CPUs are what I'd call a "technical fanfiction". It seems to have a bearing with reality, but if you watched the semi space for a few years, you'd know its just outside of the bounds of being realistic. Since people are imagining things because they enjoy doing it, no amount of explanations will stop them from doing so.

You seem to be discounting the cat videos and vast and various other frivolities on there - PC/tech related stuff is a relatively tame percentage of all that.That describes 90% of youtube.

I'm going on the speculative record with SMT3. The boring power of 2 dominance ....

Oh, so close. But no.

redgamingtech:

I was however told that Ryzen 5000 ... the socket will be called “AM5”

...with DDR5

...and pcie5.0

...and...

SMT5

Of course.

It's one more, isn'it?

NostaSeronx

Diamond Member

- Sep 18, 2011

- 3,815

- 1,294

- 136

Nah, it def power2SMT5

Of course.

It's one more, isn'it?

SMT2 -> SMT4 -> SMT16 -> SMT256 -> SMT65536 -> SMT4294967296 -> so on so forth.

DrMrLordX

Lifer

- Apr 27, 2000

- 23,121

- 13,220

- 136

Speculation aside, what the heck is the fascination with SMT4?

Because anyone who guesses SMT4 and proves to be correct gets to feel smarter than everyone else while also being unconventional.

Thunder 57

Diamond Member

- Aug 19, 2007

- 4,215

- 7,002

- 136

Because anyone who guesses SMT4 and proves to be correct gets to feel smarter than everyone else while also being unconventional.

Yup, that was about my line of thinking. Then if they turn out to be right, they can pretend to have inside knowledge or sources. All us plebs would give any such person all kinds of attention and possibly respect that they crave.

I think it's mainly that more than 2 threads per core has been done by other CPUs, in the SPARC and Power families. Those were also focused on high IO bandwidth, much like AMD's current EPYC offerings. But AMD has to design for both consumers and servers and SMT2 is a pretty good compromise.Speculation aside, what the heck is the fascination with SMT4? Because it really hasn't been done before (or at all in x86-land)? If AMD saw a reason for it, I'm sure they'd be working on it. With the massive amount of real cores available these days, I really question how much doubling threads would help outside of very specific use cases.

Some example benchmarks from 7zip on a SPARC T5, 1 core 8 threads:

| Threads | Compression (MIPS) | Decompression (MIPS) |

|---|---|---|

| 1 | 2240 | 2100 |

| 2 | 3600 | 3230 |

| 4 | 4320 | 4570 |

| 8 | 4600 | 5460 |

As you can see the benefit diminishes.

Last edited:

Speculation aside, what the heck is the fascination with SMT4? Because it really hasn't been done before (or at all in x86-land)? If AMD saw a reason for it, I'm sure they'd be working on it. With the massive amount of real cores available these days, I really question how much doubling threads would help outside of very specific use cases.

As others noted, it has been done before. I am not sure what the first implementation was. There was the UltraSPARC T1 all of the way back in 2005. That one was 279 million transistors on a 90 nm process with an area of 378 mm2 (from Wikipedia) for up to eIght 4 thread cores. There was some weirder cpu designs even earlier like the Cray MTA processors (128 hardware threads per core). The IBM power 9 does SMT4 and SMT8 now.

The early multithreaded processors really didn’t have the resources to run both single thread and multithreaded code well. The T1 was up to 8 cores with only 279 million transistors. Modern processors have billions of transistors to play with. Most people I know turned HT off on intel processors up until intel made a bunch of improvements in Haswell or Broadwell; I forget which. Even after Broadwell, it often doesn’t increase performance at all for HPC and workstation applications.

I don’t really expect AMD to do SMT4 in Zen 3. It does make some sense though. They already have a good SMT2 implementation, so extending that to 4 threads could be plausible design-wise. Also, there doesn’t seem to be a core count increase with Zen 3, so that could make up for that. It does make sense for some server applications and AMD is server first these days.

I don’t think tackling SMT4 with Zen 3 would have been their best course of action. It isn’t useful outside of niche (but very profitable) applications. We pretty much know that Zen 3 is a massive rework of the cache architecture. The CCX is going 8 core and 32 MB of L3, which is a massive change by itself. I think they are also going to increase cache bandwidth significantly to support increased floating point throughout. We pretty much already know that also, we Just don’t know how much improvement there will be. There is a lot of discussion about SMT4 because it is still a bit of an unknown. With all of the other somewhat known changes, it just seems like too much to also add SMT4. We don’t really need to go up to more threads. Perhaps when they switch to DDR5 and PCi-e 5.0, they will also increase the thread count. That may also be the time to switch the IO die to an interposer with massive L4 cache. They are still at 8 channel memory for up to 128 threads now. They are also in the strange situation where they have more IO bandwidth than memory bandwidth. That will be great for supercomputer designs; massive overkill for just about anything else. I think they will want more memory bandwidth before they increase the thread count. A super large L3 cache variant will help with that. I think the applications where Intel wins will be almost non-existent with Zen 3 unless intel really pulls a hat out of a rabbit soon.

TRENDING THREADS

-

Discussion Zen 5 Speculation (EPYC Turin and Strix Point/Granite Ridge - Ryzen 9000)

- Started by DisEnchantment

- Replies: 25K

-

Discussion Intel Meteor, Arrow, Lunar & Panther Lakes + WCL Discussion Threads

- Started by Tigerick

- Replies: 23K

-

Discussion Intel current and future Lakes & Rapids thread

- Started by TheF34RChannel

- Replies: 23K

-

-

AnandTech is part of Future plc, an international media group and leading digital publisher. Visit our corporate site.

© Future Publishing Limited Quay House, The Ambury, Bath BA1 1UA. All rights reserved. England and Wales company registration number 2008885.