-

We’re currently investigating an issue related to the forum theme and styling that is impacting page layout and visual formatting. The problem has been identified, and we are actively working on a resolution. There is no impact to user data or functionality, this is strictly a front-end display issue. We’ll post an update once the fix has been deployed. Thanks for your patience while we get this sorted.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Discussion Qualcomm Snapdragon Thread

Page 188 - Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.

CouncilorIrissa

Senior member

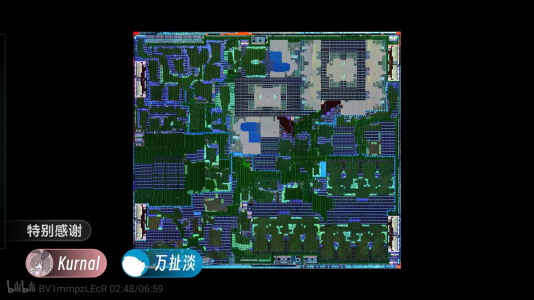

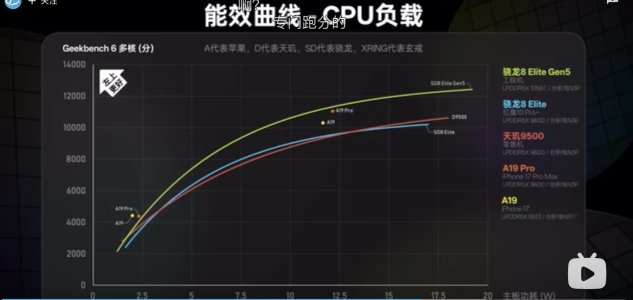

Scales further with power than a Steam Deck. lmao20 watts for 12k+ score in MTView attachment 130927

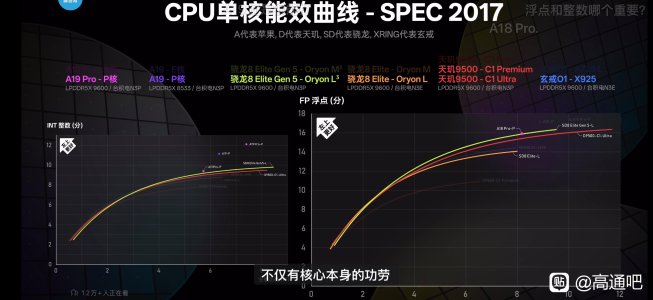

10W+ 1t package power in a phone, coming to you in 2026 I guess.GB 6 ST perf/watt View attachment 130926

adroc_thurston

Diamond Member

12W actually.10W+ 1t package power in a phone, coming to you in 2026 I guess.

poke01

Diamond Member

CrazyNVL's not gonna touch datboi either.

adroc_thurston

Diamond Member

That's the price one pays for being stuck wrt frequency.Crazy

adroc_thurston

Diamond Member

Oh wait no sorry, that's correct.The original claim was LPDDR5 of 8448 MT/s. They seem to have lost a gigaherz.

7446 was MTL.

From the IMC POV it's the same thing.not the same

DIMM vs. MrDIMM

Likely the cost of 12 MB vs 16 MB of L2 --they integrate the modem (a part which Srouji called the most complex that his team ever undertaken) which Apple does not.GB 6 ST perf/watt View attachment 130926

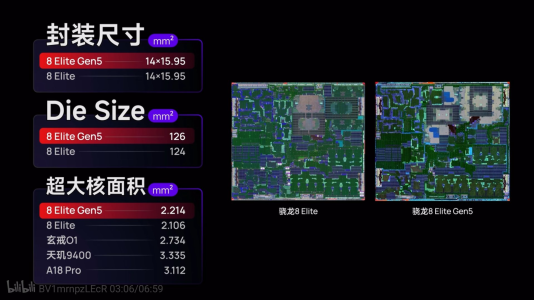

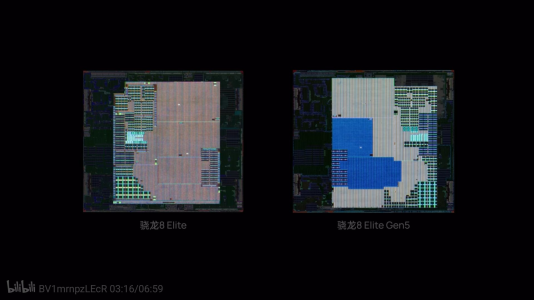

They crammed SME, 50% more GPU cache, a better modem and a better NPU into the same die size --impressive.

poke01

Diamond Member

Yeah very impressive.Likely the cost of 12 MB vs 16 MB of L2 --they integrate the modem (a part which Srouji called the most complex that his team ever undertaken) which Apple does not.

They crammed SME, 50% more GPU cache, a better modem and a better NPU into the same die size --impressive.

adroc_thurston

Diamond Member

Pretty sure N3p offers like a 4% optical shrink, but still good.Yeah very impressive.

branch_suggestion

Senior member

Gonna need an area calc on that.

poke01

Diamond Member

The CPU package will be small. These are very tiny cores for the performance they pack.Gonna need an area calc on that.

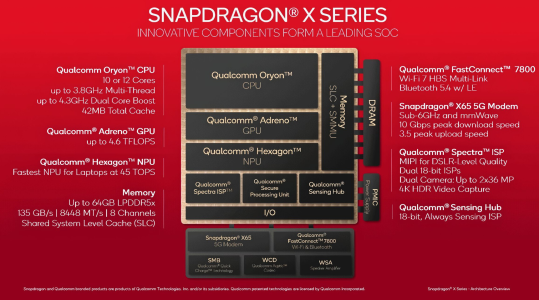

The 192b memory bus for the top SKU looks interesting. Good to see the continued march towards faster memory with both wider buses and high MT.

That gives us Apples Mx Pro/Max/Ultra, AMD's Strix Halo and the Qualcomm X2 with greater than 128bit buses on consumer hardware.

That gives us Apples Mx Pro/Max/Ultra, AMD's Strix Halo and the Qualcomm X2 with greater than 128bit buses on consumer hardware.

adroc_thurston

Diamond Member

It's only 192b for a single meme-y MoP SKU unfortunately.The 192b memory bus for the top SKU looks interesting. Good to see the continued march towards faster memory with both wider buses and high MT.

That gives us Apples Mx Pro/Max/Ultra, AMD's Strix Halo and the Qualcomm X2 with greater than 128bit buses on consumer hardware.

adroc_thurston

Diamond Member

Frequency stability.Any idea why the IPC measurement would be at 3.65GHz instead of 4.61GHz?

So pretty obvious that the X2 Elite Extreme is a binned X2 Elite. And I'm gonna guess the 12 core X2 Elite is also the same die, but binned on defects/power rather than clock rate.

I wonder what the 1T power difference is between 5.0 GHz and 4.7 GHz? How much extra power are they burning for that last 6% of clock? Were they just squeezing every drop they could while still yielding a useful number of top bin dies, or were they chasing some particular performance target? Anyone see anything out there or on the horizon that the 5 GHz part just barely beats, but the 4.7 GHz part falls short of?

I wonder what the 1T power difference is between 5.0 GHz and 4.7 GHz? How much extra power are they burning for that last 6% of clock? Were they just squeezing every drop they could while still yielding a useful number of top bin dies, or were they chasing some particular performance target? Anyone see anything out there or on the horizon that the 5 GHz part just barely beats, but the 4.7 GHz part falls short of?

adroc_thurston

Diamond Member

Wrong, it's basically a halo SKU, with MoP (and thus full memory width) and a different package.So pretty obvious that the X2 Elite Extreme is a binned X2 Elite

Yup and there's also a dedicated 6+6 die for mainstream later on.And I'm gonna guess the 12 core X2 Elite is also the same die, but binned on defects/power rather than clock rate.

yea.Anyone see anything out there or on the horizon that the 5 GHz part just barely beats, but the 4.7 GHz part falls short of?

Last edited:

TRENDING THREADS

-

Discussion Zen 5 Speculation (EPYC Turin and Strix Point/Granite Ridge - Ryzen 9000)

- Started by DisEnchantment

- Replies: 25K

-

Discussion Intel Meteor, Arrow, Lunar & Panther Lakes + WCL Discussion Threads

- Started by Tigerick

- Replies: 24K

-

Discussion Intel current and future Lakes & Rapids thread

- Started by TheF34RChannel

- Replies: 24K

-

-