Yotsugi

Golden Member

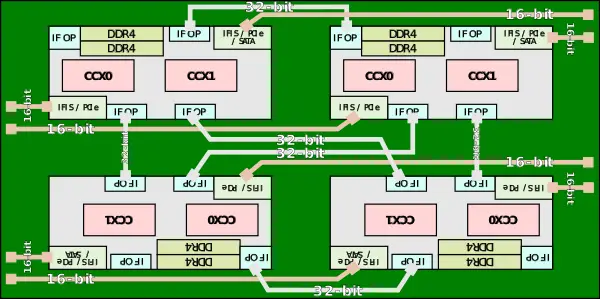

They don't.Point being the the DRAM controllers are on opposite ends of the CPU design and have interconnects to the nearest CCX.

And there's only one, dual-channel DRAM controller on Zeppelin.

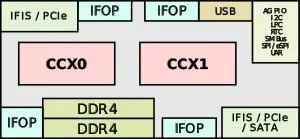

WikiChip has a Zeppelin diagram.

Go look at it or something.