The Stilt

Golden Member

- Dec 5, 2015

- 1,709

- 3,057

- 106

You compare 4-core Intel to 2-module AMD cpu's. 4-core Zen will have about 100 percent more fpu-simd resources and L2-bandwith versus two module versions.

Every module has 2-thread SIMD fpu, every Zen core will have about same resources for fpu(2-threads, L2). Only L1-bandwith will be lower but as write throughput is L2-cache limited module cores can't get full benewith from it. So 4-core Zen should be about twice as fast as 2-module const core at heavy SIMD workloads. So very close to Haswell.....

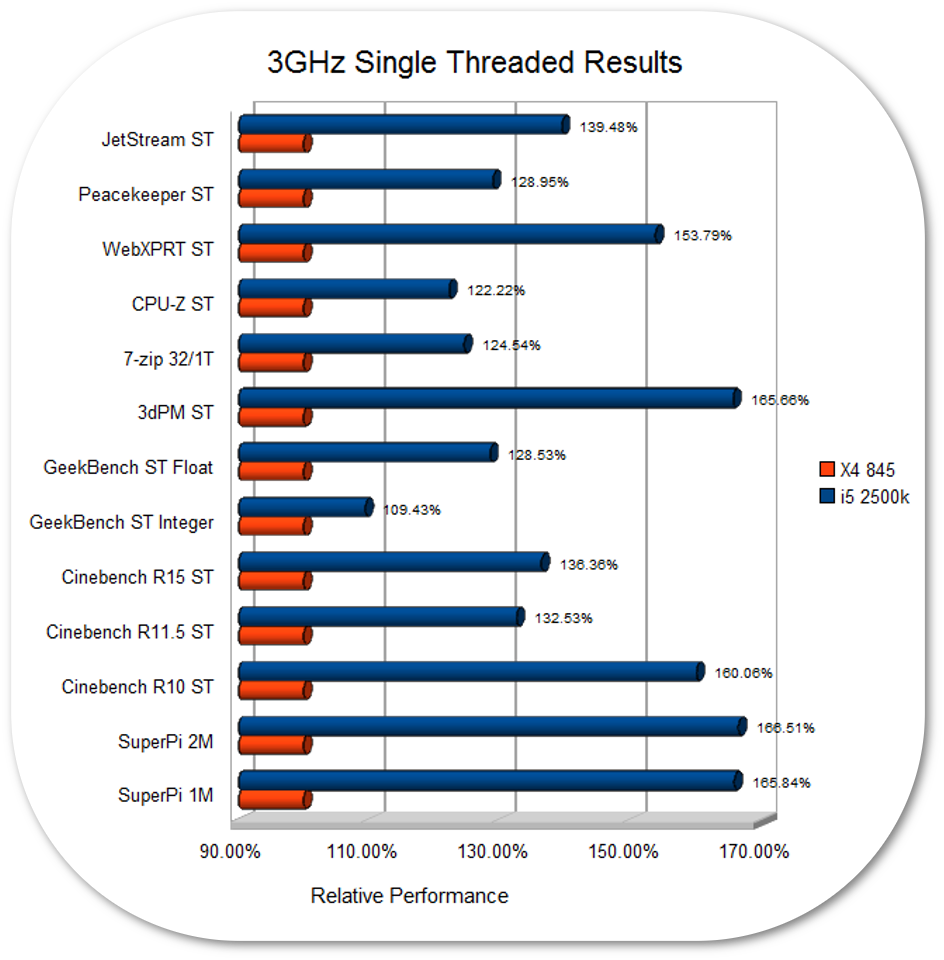

The test was ST.