The news of yesterday was an April's Fool, and at the present moment is not a secret anymore. The AIDA64 screens were fakes, but there is a kernel of truth.

First of all, A0 samples of 8 cores Zen exist, and it seems that AMD has already delivered them to its partners for the preliminary tests. The base frequency seems to be very high (3 GHz, Turbo still not enable with these ES) for a high end 8 cores CPU, also produced on a new node like the 14nm LPP FinFET of Samsung/GloFo (The first ES of Bulldozer worked at 2,8 GHz). It is a promising start.

About Zen, I can tell you some my speculations (NO OFFICIAL INFO) and some news from USA (from the same guy who told me about Zen, 3 days earlier the Official Presentation made by AMD).

If 14nm LPP will be good, Zen base frequency (8 cores version, TDP 95W) will be 3.7-3.8 GHz. Turbo 4.1-4.2 GHz. If 14nm LPP will be very good (or if AMD will commercialize a limited edition, like the Athlon Slot A 1GHz during the good old times), Zen will have a base frequency of 4 GHz (Turbo 4.2-4.3 GHz). Also, the overclockers will have a lot of fun, because of the soldered IHS!

Zen seems to be a High Performance and High Frequency uArch, like Skylake and Kaby Lake, but with some little tweak. The design team lead by Keller, as you know, has chosen to simplify some features in order to limit the Power Consumption and improve the Frequency, due to the low availability of appropriate software at the present moment (e.g. 2 x 128 Bit FMA instead of one big 256 Bit FMA SIMD). FPU units, however, will be very strong. In theory, Zen will be a monster in video games tasks (It's just an example). We can expect an IPC at Broadwell level. And if some companies want some features, AMD can do a Custom Zen CPU/APU (It has a modular design).

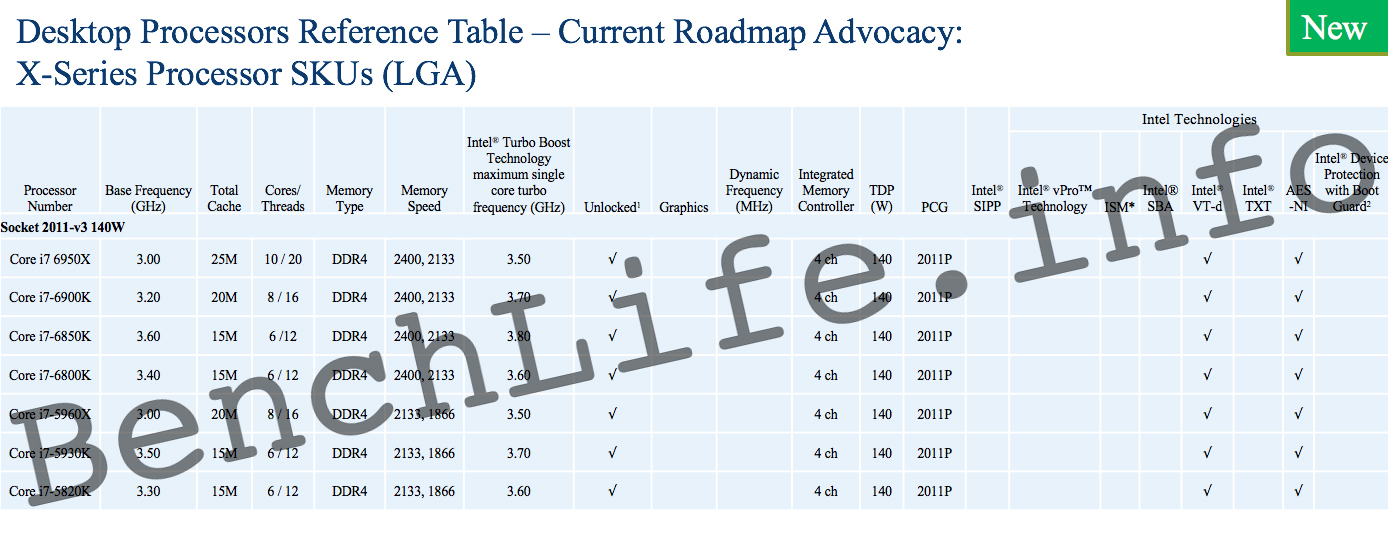

Last, but not the least, the part of the news about Intel was true. It seems that Intel will commercialize a 10 cores Broadwell-E due to its own internal Zen simulations (Intel has some data we don't know, yet, and has skilled engineers that know what they do). Zen will have 8 cores, while Broadwell-E 10 cores. So, Intel will have the “King of the Hill”, but Zen seems to be very good in the mid range of the market (AKA, gaming and enthusiast configurations).