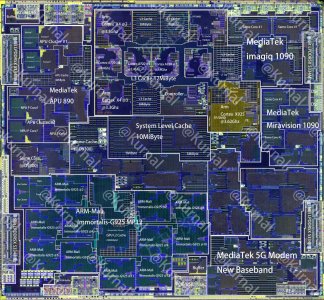

Is 1 MB per core or per cluster? If is per core, it fits since the A725 on the big cores only uses 1 MB and on the "small ones" just 512 kb.Ahem...

The maximum amount of L2 cache the Cortex A725 can be configured with is 1 MB.

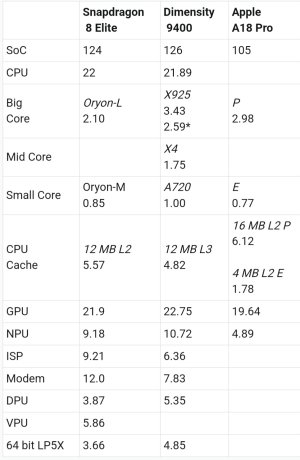

Even Dimensity 9400 only has a total of 7 MB of L2 private caches across it's 8 cores.

If is per cluster, well, time to use the L3 cache then.