- Sep 6, 2003

- 11,727

- 46

- 91

I will preface this question that I have been into computers pretty heavily from 1995 to about 2010 when I went into embedded systems and the design of multirotor flight controllers as they switched from 8bit to 32bit. Now, in 2017, back to computers and I am reading and seeing 10/14nm a possible wall for silicon.

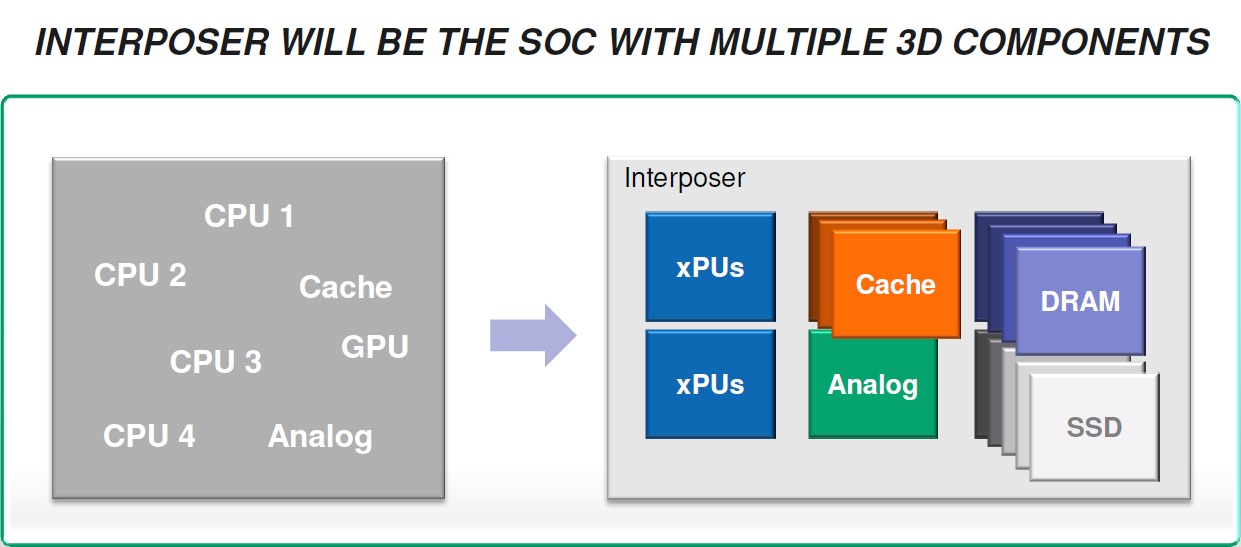

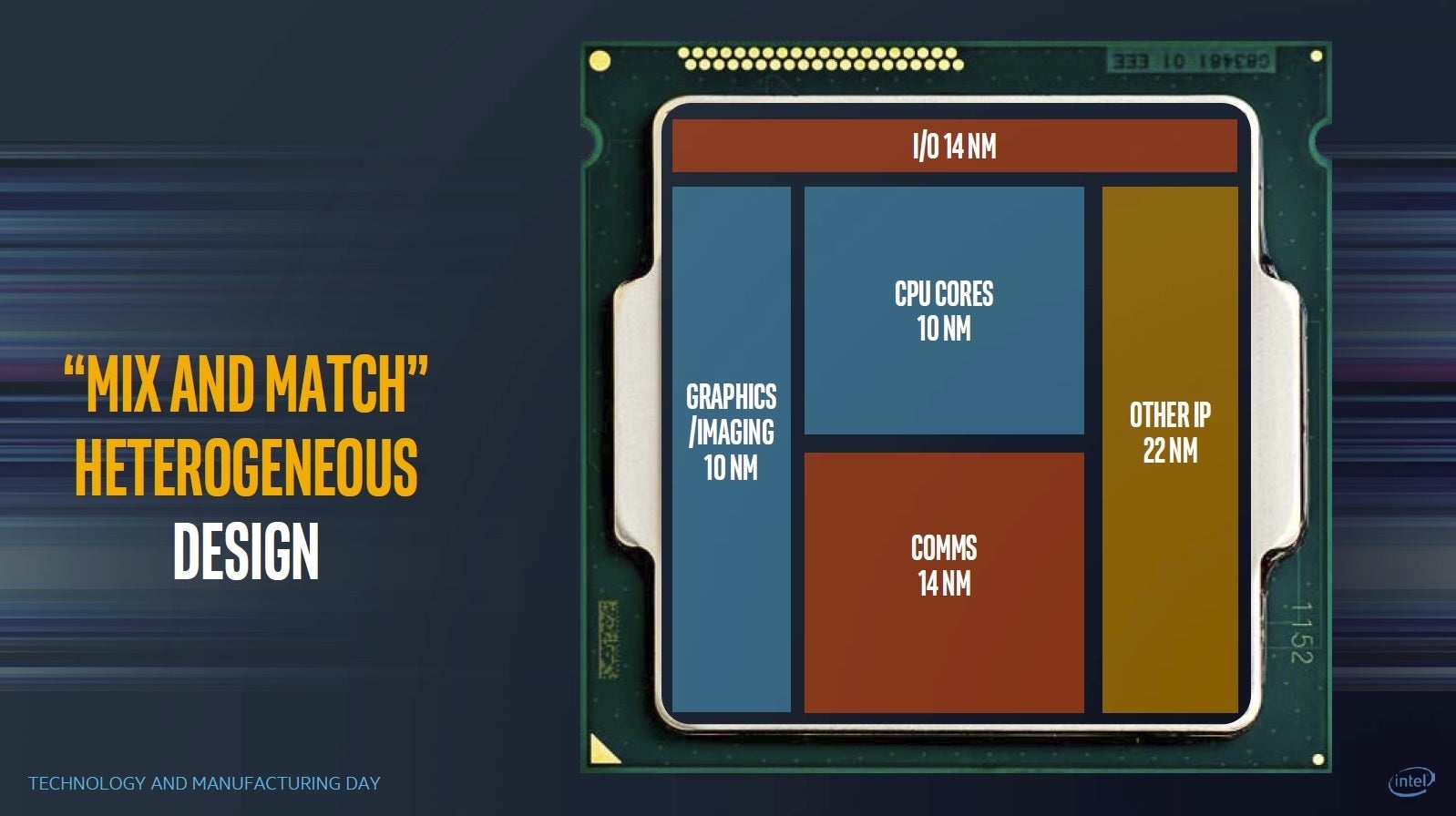

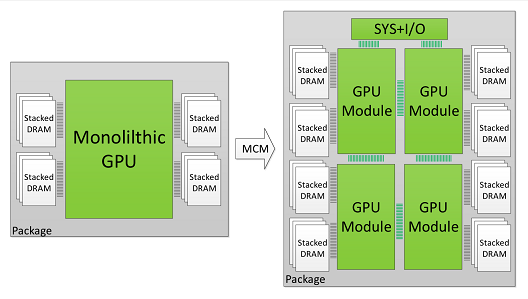

I was wondering, is 10 or 14nm the max for silicon? If so, is there some other material or hybrid material that can continue Moore's law or is it now @ 10 or 14nm cores and just adding more cores per physical cpu to get the desired effect of more power in the same space, along with other manf abilities to get power per size up?

I know there is a rather small amount of the population (with the exception of Government, R&D and the niche fields that need more power than say a i5-2500K or an i7-2600K, and they probably already have or are working on their needs) that truly needs more processing power, especially on the cpu side, but where do we go from here (as I write this from an old Lenovo T400 laptop w/ 8GB of ram and a SSD, it is a decent laptop for web browsing, lower resolution PS and AI work, smaller assembly SolidWorks design, etc. and when I need a new laptop I will probaby upgrade to a T430 or something around that) As you know, Moore's states approximately every 18mos computational power would double, but if we cannot shrink the transistors and get more per square inch (or square centimeter for the rest of the world), what is your personal opinion as I have been out of normal computers for some time (as you can see from rig in sig)?

Would definitely like to hear from you and educate me about whether I am way off or silicon still does have more life in it, say 7nm or less?

If this has been beat to death already during the times I was away, please point me to the threads if you would be so kind, thanks.

Thanks for your input,

Bob

I was wondering, is 10 or 14nm the max for silicon? If so, is there some other material or hybrid material that can continue Moore's law or is it now @ 10 or 14nm cores and just adding more cores per physical cpu to get the desired effect of more power in the same space, along with other manf abilities to get power per size up?

I know there is a rather small amount of the population (with the exception of Government, R&D and the niche fields that need more power than say a i5-2500K or an i7-2600K, and they probably already have or are working on their needs) that truly needs more processing power, especially on the cpu side, but where do we go from here (as I write this from an old Lenovo T400 laptop w/ 8GB of ram and a SSD, it is a decent laptop for web browsing, lower resolution PS and AI work, smaller assembly SolidWorks design, etc. and when I need a new laptop I will probaby upgrade to a T430 or something around that) As you know, Moore's states approximately every 18mos computational power would double, but if we cannot shrink the transistors and get more per square inch (or square centimeter for the rest of the world), what is your personal opinion as I have been out of normal computers for some time (as you can see from rig in sig)?

Would definitely like to hear from you and educate me about whether I am way off or silicon still does have more life in it, say 7nm or less?

If this has been beat to death already during the times I was away, please point me to the threads if you would be so kind, thanks.

Thanks for your input,

Bob

Last edited: