Nothingness

Diamond Member

- Jul 3, 2013

- 3,374

- 2,475

- 136

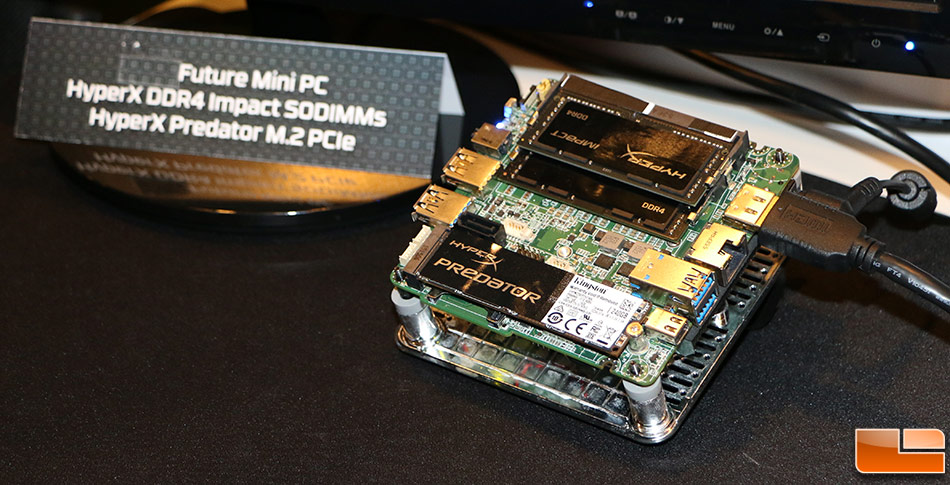

Doesn't it lack HDMI 2.0 and do HTPC-friendly MB have a workaround for this (which exists in the form of an external chip IIUC)?HTPC as in home theater PC with 4K movie playback? No, Skylake is better.

IMHO if you aim at 4k, you want HDMI 2.0.