Yeah, I used to claim it was just packaging issues too, but the PTL launch fiasco is so bad (btw Intel is claiming they have that one PTL sku out already lmao) it makes me think 18A is just chopped and that also played a part in the delays.This is just a speculation on my part, but I think there was more to the delay than a packaging issue.

It seems to me that from an array of excuses Intel narrowed down to one that would result in the least PR damage, and it is packaging.

People might think of it like Santa having this phenomenal present in the sled, but he can't deliver it because Santa is out of the red ribbons to tie around the package.

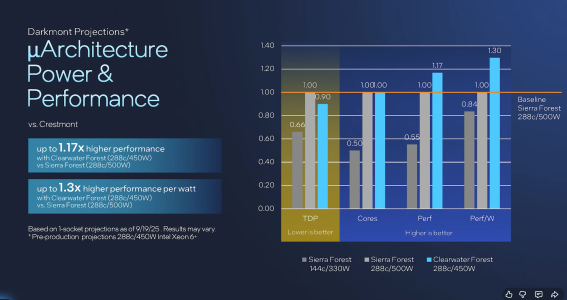

Even if the CLF die itself is small, binning for power might just be terrible.

Maybe Intel didn't want a repeat of ICL, where ICL server skus had very little to no perf/watt increase over iso core count 14nm skus.