Problem with that is segmentation.

Be it monolithic or 2xchiplets then there's only 4 memory channels for the socket which is a marketing problem for bronze/silver xeons. AMD has a similar issue with the lowest end epycs being "designed" for only 4 memory channels but you can at least still populate the extra sockets and not just have dead dimms.

If it's a new hedt socket then I can see xeon bronze and maybe silver using the new smaller socket. Big spr is big and it's a lot of silicon to waste for 6-24core cpus for customers who only really want to keep the lights flashing on their file server.

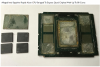

Monolithic doesn't seem like a bad idea. People have noted how much silicon is used on the spr chips for the emib logic.

Saving space on upi, emib, coherency logic, hbm controllers and also no emib silicon itself and it's complex substrate.

I'd say it compares favourably against two tiles at these core counts.