-

We’re currently investigating an issue related to the forum theme and styling that is impacting page layout and visual formatting. The problem has been identified, and we are actively working on a resolution. There is no impact to user data or functionality, this is strictly a front-end display issue. We’ll post an update once the fix has been deployed. Thanks for your patience while we get this sorted.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Discussion Intel current and future Lakes & Rapids thread

Page 550 - Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.

IntelUser2000

Elite Member

I would have to see a 12900k's performance when power limited to 45W or 65W before I would agree with that statement.

What I meant with this was that if it was a proper desktop chip meant to compete against the 5950X for example, it would have had a larger config - 6+16 or 8+16 or heck 10+16!

And a proper desktop chip would be something so they can comfortably beat the 5950X so they'll be fine until the next generation, not something they can maybe, possibly, sometimes beat the 5950X.

Only reason the 8+8 has any chance against the 5950X is because it seems Gracemont portion may turn out better than we initially expected.

8+8 is pretty much 6+8 but with the iGPU cut to add 2 more cores. In the grand scheme of things it's the 5775C. Great for some scenarios but we mostly cared about the mobile chips.

IntelUser2000

Elite Member

0+8 is a pretty weird config for an M SKU though. You'd think that if Gracemont matches expectations, 4 would be plenty for low end devices. 0+8 will have some interesting overlap with a theoretical 1+4 or similar.

Even if it was 50% faster than Tremont, which is a tremendous achievement it won't end up being anywhere near 10700K in MT.

The 10700K gets 5000 points in R20 MT while the Tremont N6005 gets 925. Maybe it'll do little better than 50% and the 4 core Gracemont gets 1400. You multiply that by 1.9x for double the cores and you end up with 2650. Realistically it'll probably need to be rated at 18W to get that or need to reduce clocks and you'll get 2300 points or so, which is less than half of the 10700K.

That puts it pretty close to the T variant of Cometlake chips. But the difference is that the N chips typically are rock solid when it comes to maintaining frequency at that power levels. So what you get under 30 second loading is pretty much what you get under 3 hour loading.

Last edited:

DrMrLordX

Lifer

0+8 is a pretty weird config for an M SKU though. You'd think that if Gracemont matches expectations, 4 would be plenty for low end devices. 0+8 will have some interesting overlap with a theoretical 1+4 or similar.

4c Gracemont would be somewhere around the computing power of some previous-gen Pentium Golds. Maybe OEMs would really prefer that, but in terms of die area and cost, an 8c SKU should be very close while offering a considerable advantage for home or corporate users that just want to be sloppy while multitasking. In the end it's a matter of what OEMs want to put in their low-end trash systems that proliferate in corporate environments and get sold to Grandma. For awhile there, you couldn't escape the little Pentium Silver systems, though I must admit it's been awhile since I've seen those outside of the Asian market.

It may well be that these SKUs are intended mostly for the Asian market. Pentium Golds may continue to be the low-end CPU of choice for OEM systems in North America and much of Europe.

What I meant with this was that if it was a proper desktop chip meant to compete against the 5950X for example, it would have had a larger config - 6+16 or 8+16 or heck 10+16!

There's limits to what Intel can do with 10ESF. We don't even have a good yield picture on it yet.

insertcarehere

Senior member

Even if it was 50% faster than Tremont, which is a tremendous achievement it won't end up being anywhere near 10700K in MT.

The 10700K gets 5000 points in R20 MT while the Tremont N6005 gets 925. Maybe it'll do little better than 50% and the 4 core Gracemont gets 1400. You multiply that by 1.9x for double the cores and you end up with 2650. Realistically it'll probably need to be rated at 18W to get that or need to reduce clocks and you'll get 2300 points or so, which is less than half of the 10700K.

That puts it pretty close to the T variant of Cometlake chips. But the difference is that the N chips typically are rock solid when it comes to maintaining frequency at that power levels. So what you get under 30 second loading is pretty much what you get under 3 hour loading.

The N6005 has 1.5MB shared L2 cache between the 4 cores while Gracemont has 4 MB shared L2 Cache per 4 core complex, so Gracemont should probably scale significantly better in MT workloads than Tremont. Since we know a 12900k gets 10.5-11k in R20MT & a 12400 gets less than 5k in R20MT, the math doesn't work out unless the Gracemont complex accounts for quite a bit above 3k or so. Nowhere near a 10700k (way lower clocks and no HT all but guarantee this), but would be more than respectable for any mobile application even without Golden Cove.

Last edited:

coercitiv

Diamond Member

The 3k+ obtained in 12900K will not translate in mobile, @IntelUser2000 estimate was based on lower power figures than what ADL-S is likely pumping through E cores to maximize throughput. I wouldn't be surprised if a 4-core complex is using 20W+ for those high CB20 scores, meaning 40W for 8 cores. Scaling back to 10W per core complex will come with a relatively small performance penalty, but a penalty nonetheless.The N6005 has 1.5MB shared L2 cache between the 4 cores while Gracemont has 4 MB shared L2 Cache per 4 core complex, so Gracemont should probably scale significantly better in MT workloads than Tremont. Since we know a 12900k gets 10.5-11k in R20MT & a 12400 gets less than 5k in R20MT, the math doesn't work out unless the Gracemont complex accounts for quite a bit above 3k or so. Nowhere near a 10700k (way lower clocks and no HT all but guarantee this), but would be more than respectable for any mobile application even without Golden Cove.

The ~2700 score @ 18W estimate seems much more realistic.

N has historically been its own die. Should be the same for whatever this is.

That's true but it's going to be awhile before OEMs quit 14 nm Atoms. Busted Big Core dies from the 2+8 and 6+8 might be enough to satisfy demand.

You have to remember, these chips don't have hyperthreading.0+8 is a pretty weird config for an M SKU though. You'd think that if Gracemont matches expectations, 4 would be plenty for low end devices. 0+8 will have some interesting overlap with a theoretical 1+4 or similar.

DrMrLordX

Lifer

That's true but it's going to be awhile before OEMs quit 14 nm Atoms.

Who in retail is still using Goldmont Plus? I can't even find any sold in AiOs or desktops in the United States like the old days. They've all switched to newer Pentium Golds; for example, the cheapest AiOs from Dell use the Pentium Gold 7505 which is a 2c/4t TigerLake. It's very much a mobile product in a desktop form factor (which is typical for cheap AiOs), but it isn't Goldmont Plus.

Who in retail is still using Goldmont Plus? I can't even find any sold in AiOs or desktops in the United States like the old days. They've all switched to newer Pentium Golds; for example, the cheapest AiOs from Dell use the Pentium Gold 7505 which is a 2c/4t TigerLake. It's very much a mobile product in a desktop form factor (which is typical for cheap AiOs), but it isn't Goldmont Plus.

Laptops mainly.

Even if it was 50% faster than Tremont, which is a tremendous achievement it won't end up being anywhere near 10700K in MT.

The 10700K gets 5000 points in R20 MT while the Tremont N6005 gets 925. Maybe it'll do little better than 50% and the 4 core Gracemont gets 1400. You multiply that by 1.9x for double the cores and you end up with 2650. Realistically it'll probably need to be rated at 18W to get that or need to reduce clocks and you'll get 2300 points or so, which is less than half of the 10700K.

That puts it pretty close to the T variant of Cometlake chips. But the difference is that the N chips typically are rock solid when it comes to maintaining frequency at that power levels. So what you get under 30 second loading is pretty much what you get under 3 hour loading.

Don't forget N6005 does not support AVX2.

Last edited:

Don't forget N6005 does not support AVX2.

No guaranties that these new SKUs will support it either, Intel would not want to sell cheapo 8C with potent FP performance and power efficiency.

No guaranties that these new SKUs will support it either, Intel would not want to sell cheapo 8C with potent FP performance and power efficiency.

Intel did leave AVX2 enabled on the Tiger Lake Pentium and Celeron. There's even a Celeron embedded model that Ark claims has AVX-512 but that might not be true.

My guess is that the 0+8 would be Atom embedded; 1+4 be Pentium Gold and 0+4 and 0+2 be Pentium Silver and Celeron. They can always make a native die too or later.

I hope not, losing enough P cores on 6+8 dice to create a separate 0+8 SKU would be bad news from a process perspective.Could even be the 6+8 die although it would have to use the P packing instead.

Hulk

Diamond Member

I hope not, losing enough P cores on 6+8 dice to create a separate 0+8 SKU would be bad news from a process perspective.

It also seems highly unlikely from a statistical point-of-view to have defects in all 6 P cores and no defects in any of the 8 e cores.

I believe Ian write there will be 3 dies, 8+8 desktop, 6+4 mobile, and 2+8 ultramobile.

The 2+8 configuration looks to be a great part if we are looking at Gracemont being super-efficient, equal-to-Skylake performing cores.

It also seems highly unlikely from a statistical point-of-view to have defects in all 6 P cores and no defects in any of the 8 e cores.

I believe Ian write there will be 3 dies, 8+8 desktop, 6+4 mobile, and 2+8 ultramobile.

The 2+8 configuration looks to be a great part if we are looking at Gracemont being super-efficient, equal-to-Skylake performing cores.

No, four known dies:

8+8+1 desktop

6+0+1 desktop

6+8+2 mobile

2+8+2 mobile

And now possibly a fifth 0+8+? N die.

It also seems highly unlikely from a statistical point-of-view to have defects in all 6 P cores and no defects in any of the 8 e cores.

But the 0+8 would also be a extremely low volume product too. There's other considerations like stable clock speed or the IGP (Intel hasn't IIRC sold an U product without the IGP enabled... officially anyway)

DrMrLordX

Lifer

Laptops mainly.

Okay I found two Goldmont Plus Refresh laptops on Dell's site, so they are still selling them. N4020 and N5030.

But the 0+8 would also be a extremely low volume product too. There's other considerations like stable clock speed or the IGP (Intel hasn't IIRC sold an U product without the IGP enabled... officially anyway)

Wait, why would 0+8 be low volume? Yields on such a tiny chip should be pretty high, and the Asian market would eat it up like mad.

Wait, why would 0+8 be low volume? Yields on such a tiny chip should be pretty high, and the Asian market would eat it up like mad.

I would think that if there is a fifth die, it would be 0+4+1. The 0+8 would only be busted P core dies with good E dies, which yes would be statistically rare.

DrMrLordX

Lifer

I would think that if there is a fifth die, it would be 0+4+1. The 0+8 would only be busted P core dies with good E dies, which yes would be statistically rare.

I would say "we'll see then", but likely we won't, since a discount die like that will probably be sold in downmarkets almost exclusively. Or as a replacement for Goldmont Plus Refresh.

Hulk

Diamond Member

No, four known dies:

8+8+1 desktop

6+0+1 desktop

6+8+2 mobile

2+8+2 mobile

And now possibly a fifth 0+8+? N die.

Where did you read about the 6+1 die? I didn't know about this.

Where did you read about the 6+1 die? I didn't know about this.

It's been leaked for ages, but Intel officially mentions it in their developer guide.

Game Dev Guide for 12th Gen Intel Core Processor Hybrid Architecture

The 12th Gen Intel© Core™ processor is a new performance hybrid architecture that combines two core types.

Anyway, regarding the rumored N SKU, I doubt it uses any harvested dies from M or P. Historically, N also has some cost optimization like single channel memory, less IO, etc. Curious to see how they'll market it though. The main market for those is probably Chromebooks, for which 8c seems overkill, and confusing competition with, say 1+4.

IntelUser2000

Elite Member

The chance that Intel will use P/S dies for N are slim to none.

-Astronomically low chance that only Golden Cove portion will fail and nowhere else. Not the Gracemont portion, not the caches, and not the uncore.

-Disabled die means you still end up with the larger physical die. In case of the N chips, the sheer physical size of the P/S dies will limit how small packaging can be.

-They'd have to go intentionally disable some of the GPU part so it doesn't cannibalize the rest. Also the PCI Express and the uncore. Why, when you can just make a separate N die?

-Intel knows how to make multiple dies even though the volume is pretty much in the hobbyist grade range. They made 6 or so different dies for Atom in the 45nm generation. I doubt some dies sold above 10K units.

Disabling dies to make totally new lineup is a 1998 thing. Hello! It's 2021!

@diediealldie I believe Gracemont will gain some from enabling AVX. But that amount will be small. From what I can gather, there's zero from AVX2. AVX gains might be 5%, maybe at best 10%. Even then, any gain from "floating point units" may be due to the fact that they enhanced the dataflow on the FP side, not so much as the 256-bit width and registers AVX offers.

Also, I don't believe caches benefitted Cinebench to any measurable degree. If Gracemont 10W does better than my estimations it'll be purely due to the fact that it's a better architecture than I expected.

That should be a pleasant surprise for the pro-x86 guys as well. Gracemont may end up being a great demonstration that implementation and creativity of the human mind can more than make up for a possibly deficient ISA. Also, ARM isn't just about the ISA but it has a massive industry support behind it. You put more people to work, you have a better chance of making it turn out better. Simple as that.

-Astronomically low chance that only Golden Cove portion will fail and nowhere else. Not the Gracemont portion, not the caches, and not the uncore.

-Disabled die means you still end up with the larger physical die. In case of the N chips, the sheer physical size of the P/S dies will limit how small packaging can be.

-They'd have to go intentionally disable some of the GPU part so it doesn't cannibalize the rest. Also the PCI Express and the uncore. Why, when you can just make a separate N die?

-Intel knows how to make multiple dies even though the volume is pretty much in the hobbyist grade range. They made 6 or so different dies for Atom in the 45nm generation. I doubt some dies sold above 10K units.

Disabling dies to make totally new lineup is a 1998 thing. Hello! It's 2021!

@diediealldie I believe Gracemont will gain some from enabling AVX. But that amount will be small. From what I can gather, there's zero from AVX2. AVX gains might be 5%, maybe at best 10%. Even then, any gain from "floating point units" may be due to the fact that they enhanced the dataflow on the FP side, not so much as the 256-bit width and registers AVX offers.

Also, I don't believe caches benefitted Cinebench to any measurable degree. If Gracemont 10W does better than my estimations it'll be purely due to the fact that it's a better architecture than I expected.

That should be a pleasant surprise for the pro-x86 guys as well. Gracemont may end up being a great demonstration that implementation and creativity of the human mind can more than make up for a possibly deficient ISA. Also, ARM isn't just about the ISA but it has a massive industry support behind it. You put more people to work, you have a better chance of making it turn out better. Simple as that.

Last edited:

The chance that Intel will use P/S dies for N are slim to none.

-Astronomically low chance that only Golden Cove portion will fail and nowhere else. Not the Gracemont portion, not the caches, and not the uncore.

The bulk of the volume will presumably be the 0+4 and 0+2. Which would be a lot more likely to happen than the 0+8 and at Intel's volume could very well be enough to satisfy demand when the bulk of Atom supply will be 14 nm for several more years. Doesn't mean they aren't doing an N die but it looks to be an opportunity to use stuff they would otherwise throw away.

-Disabled die means you still end up with the larger physical die. In case of the N chips, the sheer physical size of the P/S dies will limit how small packaging can be.

Packaging size doesn't appear to be an issue, given that the Tremont Atom's package looks bigger than UP4.

-They'd have to go intentionally disable some of the GPU part so it doesn't cannibalize the rest. Also the PCI Express and the uncore. Why, when you can just make a separate N die?

That's another place they could yield chips from - GPUs with only 32 EUs available.

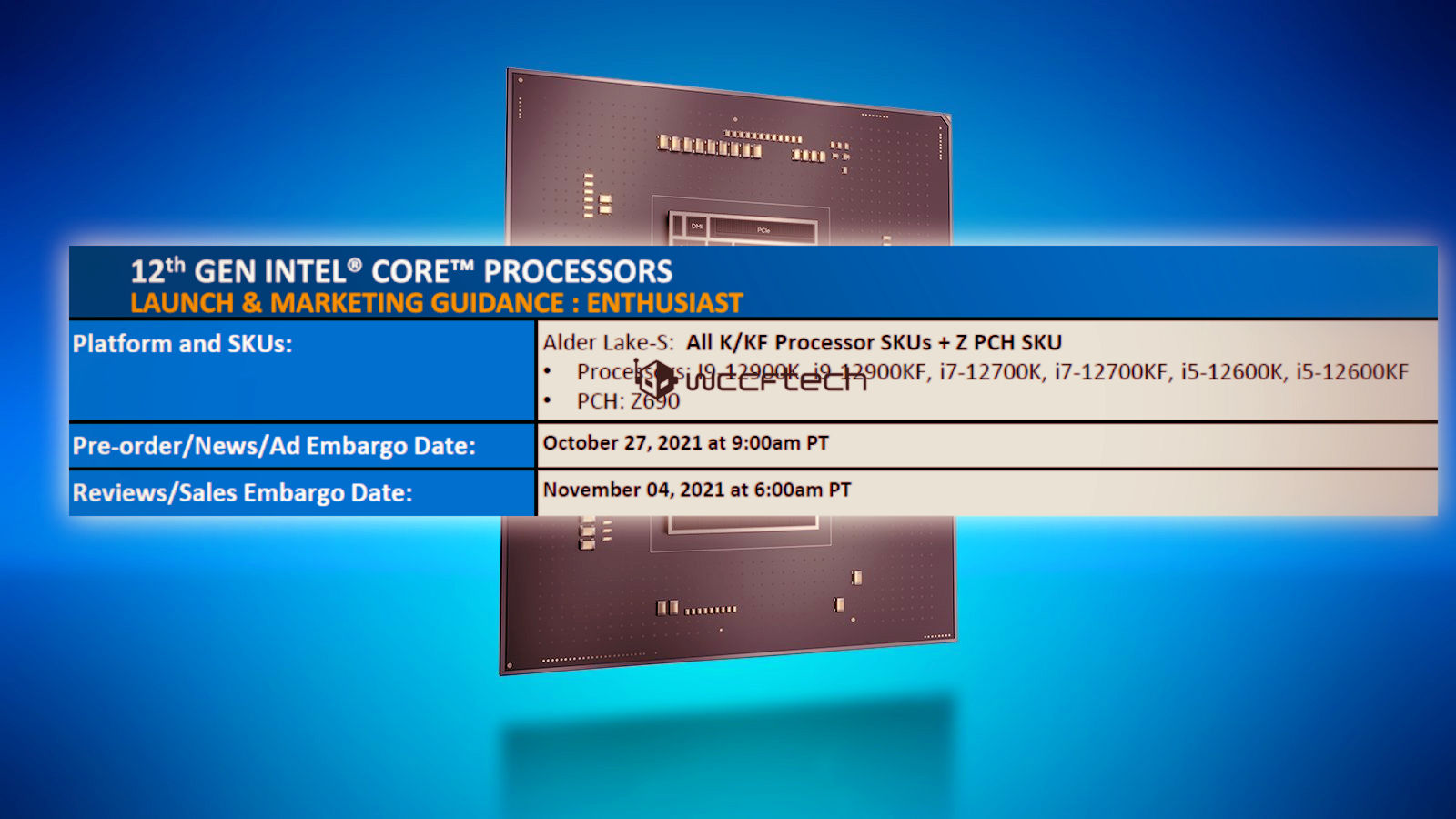

Intel Alder Lake announcement and preorders confirmed for October 27th, launch on November 4th - VideoCardz.com

Intel launch date confirmed: November 4th Wccftech shares information on embargo dates for the upcoming Intel 12th Gen Core series. Intel is to announce Alder Lake desktop processors on October 27th. This is the embargo date that has been listed in the document that has been leaked today...

Further confirmation that the launch is on the 27th and they've decided on Nov 4th for the release.

TRENDING THREADS

-

Discussion Zen 5 Speculation (EPYC Turin and Strix Point/Granite Ridge - Ryzen 9000)

- Started by DisEnchantment

- Replies: 25K

-

Discussion Intel Meteor, Arrow, Lunar & Panther Lakes + WCL Discussion Threads

- Started by Tigerick

- Replies: 25K

-

Discussion Intel current and future Lakes & Rapids thread

- Started by TheF34RChannel

- Replies: 24K

-

-