coercitiv

Diamond Member

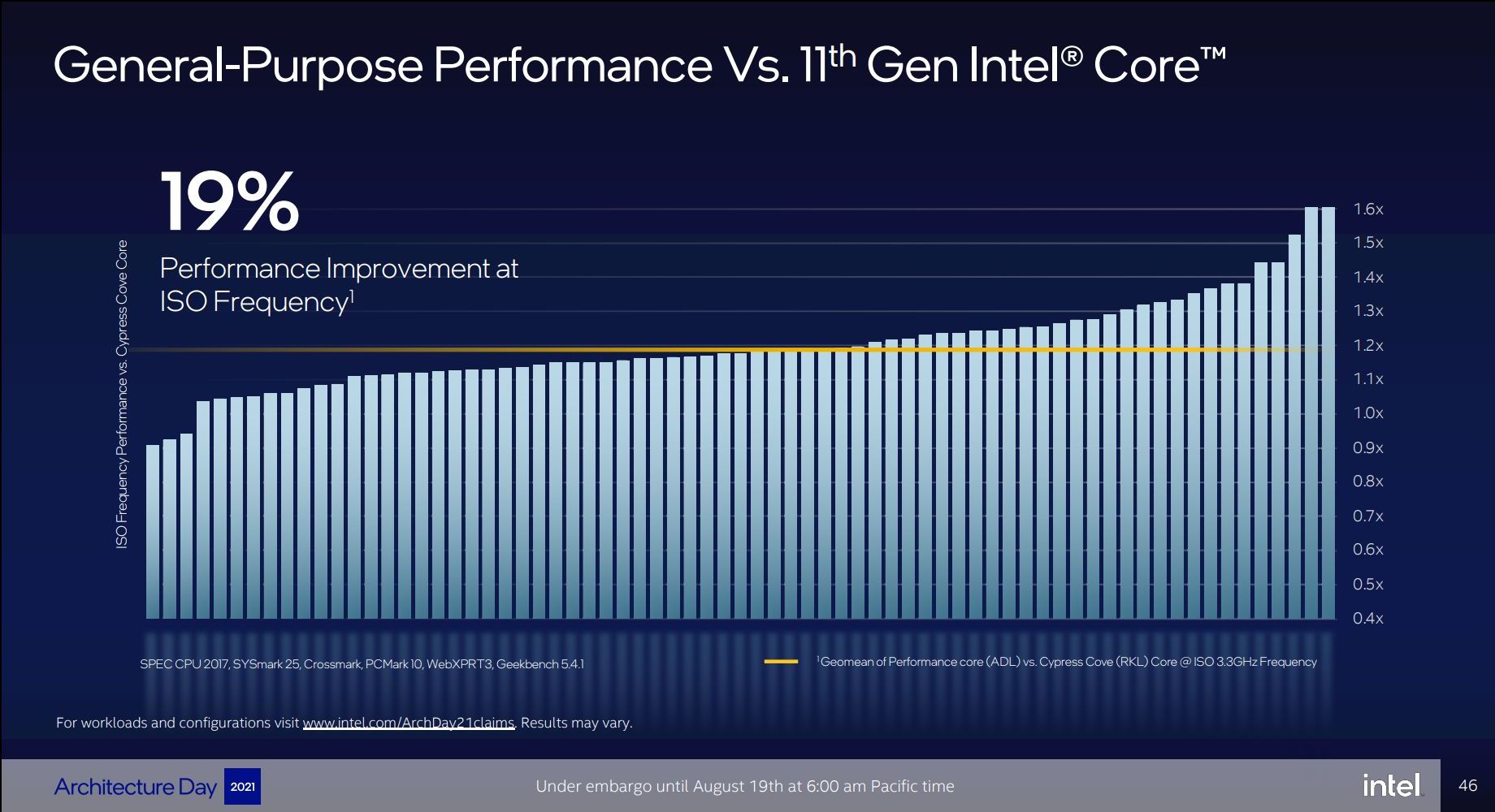

In the last two weeks people discovered there's such a thing as PL4 for Intel CPUs. We are still in the process of acknowledging (as a group) the major difference between continuous power and peak power consumption for both modern PC power supplies and VRM stages.Dealing with a nasty head cold. Can someone kind enough please give me the cliff notes of the last 1-2 weeks of Intel Alderlake info? Are we still A GO for a October launch?

As a general rule of thumb, as long as you see people arguing about power consumption in this thread it means there have been no further developments/leaks about launch timeline and/or performance. Get well soon.