Discussion Intel current and future Lakes & Rapids thread

Page 451 - Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Also, what ever the next version of Windows is, it's not new. It'll just be a branch of Win10, AFAICT. I haven't seen anything about low level changes. So, still the stinking layered up mess of services and interfaces built on the ever aging NT substructure.About ADL scheduling:

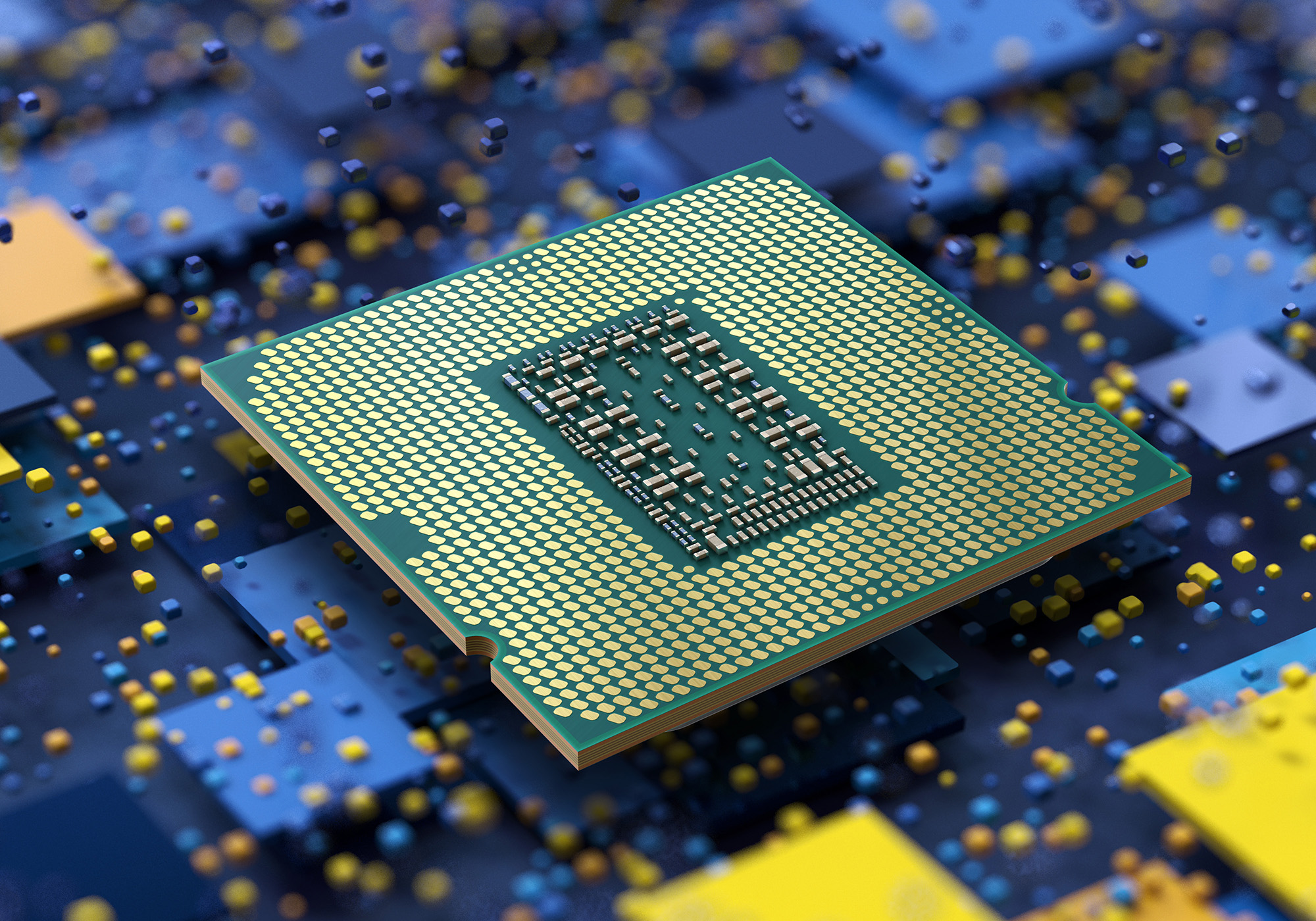

Intel 10nm Alder Lake Desktop CPUs Launching During Halloween 2021, Will Feature Support On New LGA 1700 Socket Motherboards

Intel's 12th Generation Alder Lake K-series desktop CPUs based on the 10nm Enhanced SuperFin architecture are expected to launch in October.wccftech.com

It is BS because:

Quote above coming form Microsoft and not from some dubious source. The scheduler is already working perfectly fine, which you can see when you happen to have a Windows big.LITTLE machine (perhaps excluding Lakefield)

I also posted a picture of the task manager, showing the system services on the little cores, while the big cores are power gated - except the one big core, which running the foreground app here

The Windows scheduler added support for heterogenous scheduling which took into account the app intent for scheduling on big.LITTLE architectures.

By app intent, I mean Windows tries to provide a quality of service for apps by tracking threads which are running in the foreground (or starved of CPU) and ensuring those threads always run on the big core. Whereas the background tasks, services, and other ancillary threads in the system run on the little cores. (As an aside, you can also programmatically mark your thread as unimportant which will make it run on the LITTLE core.)

Work on Behalf: In Windows, a lot of work for the foreground is done by other services running in the background. E.g. In Outlook, when you search for a mail, the search is conducted by a background service (Indexer). If we simply, run all the services on the little core, then the experience and performance of the foreground app will be affected. To ensure, that these scenarios are not slow on big.LITTLE architectures, Windows actually tracks when an app calls into another process to do work on its behalf. When this happens, we donate the foreground priority to the service thread and force run the thread in the service on the big core.

Quote above coming form Microsoft and not from some dubious source. The scheduler is already working perfectly fine, which you can see when you happen to have a Windows big.LITTLE machine (perhaps excluding Lakefield)

I also posted a picture of the task manager, showing the system services on the little cores, while the big cores are power gated - except the one big core, which running the foreground app here

Last edited:

Hulk

Diamond Member

- Oct 9, 1999

- 5,422

- 4,151

- 136

So the next version of Window will either have big scheduler changes or none at all for Big/Little.

More importantly Microsoft needs to make Windows easily customizable. Like being able to remove "3D Objects" or "Quick Launch" or a number of other apps forced on us removeable with a single right-click delete action. Stop adding garbage, it's just an OS that hosts the programs that do the real work.

More importantly Microsoft needs to make Windows easily customizable. Like being able to remove "3D Objects" or "Quick Launch" or a number of other apps forced on us removeable with a single right-click delete action. Stop adding garbage, it's just an OS that hosts the programs that do the real work.

dullard

Elite Member

- May 21, 2001

- 26,196

- 4,869

- 126

The key being that Alder Lake isn't big.LITTLE. Alder Lake is big.Medium (I refuse to use Intel's big.bigger terminology). Thus the need for changes to the scheduler. You are correct that Windows has had big.LITTLE for quite some time. But that isn't what Alder Lake uses or what Alder Lake is intended for.It is BS because:

Quote above coming form Microsoft and not from some dubious source. The scheduler is already working perfectly fine, which you can see when you happen to have a Windows big.LITTLE machine (perhaps excluding Lakefield)

I also posted a picture of the task manager, showing the system services on the little cores, while the big cores are power gated - except the one big core, which running the foreground app here

Hulk

Diamond Member

- Oct 9, 1999

- 5,422

- 4,151

- 136

The key being that Alder Lake isn't big.LITTLE. Alder Lake is big.Medium (I refuse to use Intel's big.bigger terminology). Thus the need for changes to the scheduler. You are correct that Windows has had big.LITTLE for quite some time. But that isn't what Alder Lake uses or what Alder Lake is intended for.

Do we know if the scheduler is currently only optimized for Big/Little or if it's for heterogeneous CPU's in general? If it's the latter then ADL should be fine.

itsmydamnation

Diamond Member

- Feb 6, 2011

- 3,146

- 4,031

- 136

how does big medium change anything, its only if you had big medium little would you do something different.

IE. list the exact use case where the scheduling method for big little would be different for big medium.

IE. list the exact use case where the scheduling method for big little would be different for big medium.

Hulk

Diamond Member

- Oct 9, 1999

- 5,422

- 4,151

- 136

how does big medium change anything, its only if you had big medium little would you do something different.

IE. list the exact use case where the scheduling method for big little would be different for big medium.

I was thinking the same thing but am not by any means an expert on this, which is why I posed the question. The only think I can think is that if part of the scheduler strategy is to assign the smaller cores to the OS most of the time, this could be overkill for medium cores.

But as I said I really don't know what the hell I'm talking about. But I find this topic very interesting.

The key being that Alder Lake isn't big.LITTLE. Alder Lake is big.Medium (I refuse to use Intel's big.bigger terminology). Thus the need for changes to the scheduler. You are correct that Windows has had big.LITTLE for quite some time. But that isn't what Alder Lake uses or what Alder Lake is intended for.

This does not change anything. They key here is, that the heterogenous scheduler is aware of different performance points - if you call this big.LITTLE, big.bigger or big.Medium is irrelevant for the scheduler.

As itsmydamnation was pointing out above as well, the scheduling method/heuristic stays the same.

Magic Carpet

Diamond Member

- Oct 2, 2011

- 3,477

- 234

- 106

A couple of questions guys, why Rocket Lake S doesn’t support fivr since it’s based on post Icelake tech that does? And second, what is Intel’s next desktop processor (well minus the Tiger Lake limited edition bga part) with avx512? Thanks.

coercitiv

Diamond Member

- Jan 24, 2014

- 7,506

- 17,946

- 136

Sure it does, changing the name from small to medium brings a 10-15% performance uplift at the very least. You're new around here, aren't you? Let me give you the talking points:This does not change anything.

- First we have a discussion about how most people don't really require more than a 4c/8t CPU for their daily computing needs, since any more cores would not impact perceived performance by a significant margin. Multitasking is way overrated.

- Then we have a discussion about how most people could benefit from a hybrid architecture and QoS aware scheduler that would surely impact perceived performance on the "resource starved" 4-core CPU that was more than good enough for multitasking just a month ago.

Asterox

Golden Member

- May 15, 2012

- 1,062

- 1,876

- 136

It is hard to find a words for this. Hm, lost in the woods of smoothly video playback. Completely useless, "in reality that PC also could be a AMD Ryzen PC".It is absurd for a company like Intel, to do such useless "imagine that it is Alder Lake PC and laptop".

Windows scheduler supports big.Little, they needed that for the Surface Pro X and i dont think big.MEDIUM changes anything, but ARM is going big.MEDIUM.Little with X1-A78-A55 and X2-A710-A510, so Windows will have to detect and support that more sooner than late. So if scheduler changes are needed they will come.

My only real question here is that if the scheduler knows what to do when there are little cores and big cores with HT. Or how well the thread affinity will work on x86 in a big.Little configuration when apps dont even consider that to be a thing. Because i now think that, for example, a game, should only be run on the big cores and no thread should be assigned to a little core. At first i trought that some small tasks could be assigned to small cores, but that may drag everything down really.

My only real question here is that if the scheduler knows what to do when there are little cores and big cores with HT. Or how well the thread affinity will work on x86 in a big.Little configuration when apps dont even consider that to be a thing. Because i now think that, for example, a game, should only be run on the big cores and no thread should be assigned to a little core. At first i trought that some small tasks could be assigned to small cores, but that may drag everything down really.

Last edited:

And this is how we get from not needing 6-8 classic cores on a modern desktop, but needing 6+ hybrid cores with additional scheduler optimizations on top to make everything work "faster". You see, this is why YOU don't work in Marketing, you common sense engineer! /s

And the irony is, that the desktop hybrid solution from Intel is not born from the fact, that Intel sees a particular advantage for desktops but it is here, because Intel was unable to reach their power and area targets with just large cores alone, because they are so highly inefficient - both from area and power perspective. So they make a virtue out of necessity.

Hulk

Diamond Member

- Oct 9, 1999

- 5,422

- 4,151

- 136

It is hard to find a words for this. Hm, lost in the woods of smoothly video playback. Completely useless, "in reality that PC also could be a AMD Ryzen PC".It is absurd for a company like Intel, to do such useless "imagine that it is Alder Lake PC and laptop".

Did you hear? They're "eggs-za-cuting."

uzzi38

Platinum Member

- Oct 16, 2019

- 2,747

- 6,657

- 146

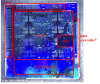

SPR die shot.

Up to 15 cores per die, so a max config of 60 cores assuming all of them are enabled.

Up to 15 cores per die, so a max config of 60 cores assuming all of them are enabled.

SPR die shot.

Up to 15 cores per die, so a max config of 60 cores assuming all of them are enabled.

The thing labeled HBM controller is almost certainly just the (DDR5) memory PHY.

SPR die shot.

Up to 15 cores per die, so a max config of 60 cores assuming all of them are enabled.

60 cores on 10 nm. . . I'm guessing base clocks well below 2 GHz or crazy high TDPs. Maybe SKUs in either direction?

ashFTW

Senior member

- Sep 21, 2020

- 331

- 252

- 146

That die shot is obviously incorrect, @ashFTW already confirmed multiple times that SPR is 80 cores based on physical evidence.

i revised it to 72 cores. I still believe that to be true, unless Intel only made one tile that has to work in both x2 and x4 configurations, in which case more I/O and mem controllers have to be put on each tile, reducing the number of cores that it can be accommodate.

uzzi38

Platinum Member

- Oct 16, 2019

- 2,747

- 6,657

- 146

...i revised it to 72 cores. I still believe that to be true, unless Intel only made one tile that has to work in both x2 and x4 configurations, in which case more I/O and mem controllers have to be put on each tile, reducing the number of cores that it can be accommodate.

I'm truly speechless.

i revised it to 72 cores. I still believe that to be true, unless Intel only made one tile that has to work in both x2 and x4 configurations, in which case more I/O and mem controllers have to be put on each tile, reducing the number of cores that it can be accommodate.

If you look at the die shot the bottom area doesn't look like an extra row of cores. I suppose it's possible that the die used is very old and the final version has 76 (72).

I think there will be a 2 die configuration for Xeon W/HEDT but that would be quad channel.

ashFTW

Senior member

- Sep 21, 2020

- 331

- 252

- 146

i revised it to 72 cores. I still believe that to be true, unless Intel only made one tile that has to work in both x2 and x4 configurations, in which case more I/O and mem controllers have to be put on each tile, reducing the number of cores that it can be accommodate.

That would be a pretty lazy thing to do, given Intel in the past has made several die sizes for each Xeon generation.

SPR supports uncore of 8 DDR5, and 80 PCIe 5.0, and up to 4 UPI. Let’s look at the options to achieve this in 2 and 4 tiles.

Tile A: all core

Tile B: half of uncore, rest core

Tile C: one fourth of uncore, rest core

to achieve medium and small configurations: two B tiles

to achieve larger configuration: 1) two A and 2 B tiles 2) four C tiles, or 3) four B tiles

if Intel only made the B tile, then the max cores with 4 tiles will be close to 60. If they made B and C, or A and B, they can go up to 72.

Lets wait and see.

Last edited:

So you think it is possible Intel taped out, produced a full set of masks, and manufactured a 15 core tile and then scrapped that and started all over again with a larger 19 core design? That is... highly unlikely.If you look at the die shot the bottom area doesn't look like an extra row of cores. I suppose it's possible that the die used is very old and the final version has 76 (72).

I think there will be a 2 die configuration for Xeon W/HEDT but that would be quad channel.

It's not lazy at all. The whole point of tiled design is reuse. The design and mask costs for newer manufacturing nodes are prohibitive unless you can achieve sufficient volume. Monolithic SoCs can only scale to a certain point and then you're forced to tile. I don't think Intel is disaggregating at all here, they're just designing specifically for multi-chip modules using advanced packaging techniques. Every SPR tile has 15 cores plus one quarter of the uncore stuff. A 4-tile package will have a maximum of exactly 60 cores.That would be a pretty lazy thing to do, given Intel in the past has made several die sizes for each Xeon generation.

SPR supports uncore of 8 DDR5, and 80 PCIe 5.0, and up to 4 UPI. Let’s look at the options to achieve this in 2 and 4 tiles.

Tile A: all core

Tile B: half of uncore, rest core

Tile C: one fourth of uncore, rest core

to achieve medium and small configurations: two B tiles

to achieve larger configuration: 1) two A and 2 B tiles 2) four C tiles, or 3) four B tiles

if Intel only made the B tile, then the max cores with 4 tiles will be close to 60. If they made B and C, or A and B, they can go up to 72.

Lets wait and see.

That being said, I find it interesting that Intel isn't using a single stepping for the tiles here. There are at least two that are sort of mirror images of each other—one with the memory controller on the left side and one with it on the right.

edit to add links to original image sources:

大IC微世界 Bilibili 2021-04-27

結城安穗-YuuKi_AnS Bilibili 2021-05-17

結城安穗-YuuKi_AnS Bilibili 2021-05-23

Raichu @OneRaichu Twitter 2021-06-05 (linked above)

Last edited:

TRENDING THREADS

-

Discussion Zen 5 Speculation (EPYC Turin and Strix Point/Granite Ridge - Ryzen 9000)

- Started by DisEnchantment

- Replies: 25K

-

Discussion Intel Meteor, Arrow, Lunar & Panther Lakes + WCL Discussion Threads

- Started by Tigerick

- Replies: 24K

-

Discussion Intel current and future Lakes & Rapids thread

- Started by TheF34RChannel

- Replies: 23K

-

-

AnandTech is part of Future plc, an international media group and leading digital publisher. Visit our corporate site.

© Future Publishing Limited Quay House, The Ambury, Bath BA1 1UA. All rights reserved. England and Wales company registration number 2008885.