Pretty sure we will never see ADM on any of Intels GT2 SKUs for MTL and ARL. If there is a GT3 for ARL with 320EU or even 384EUs this could be an option. In the older ARL-P roadmap it sounded like ADM will be exclusive to GT3 models to maximize performance (GT3 N3 with ADM to maximize performance). ARL GT2 with 192EUs I don't think we will see this.

-

We’re currently investigating an issue related to the forum theme and styling that is impacting page layout and visual formatting. The problem has been identified, and we are actively working on a resolution. There is no impact to user data or functionality, this is strictly a front-end display issue. We’ll post an update once the fix has been deployed. Thanks for your patience while we get this sorted.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Discussion Intel current and future Lakes & Rapids thread

Page 856 - Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.

lightisgood

Senior member

Intel 17th Gen CPUs to Get Rentable Units: Why Hyper-Threading is Going Away | Hardware Times

Intel’s adoption of the hybrid core architecture has significantly changed the roadmap of the PC chipmaking industry. More and more applications are now taking advantage of the “secondary” low-power E-cores to boost performance and efficiency. This approach has its shortcomings, which Intel...

www.hardwaretimes.com

www.hardwaretimes.com

Intel is going to dynamic thread splitting...

I guess that the Slipstreame 2.0 will come, because E-core is best choice for speculative precomputation.

I'd prefer to see av1 ancoding on inel gt before any of this tbh

Meteor Lake supports AV1 encoding, it's a newer media version of Arc Alchemist. It's a standalone lower clocked Media GT with 2x decode units and 2x encode units.

igor_kavinski

Lifer

Very interesting concept. SMT on steroids if they can somehow reduce P-core to E-core communication latency to bare minimum.Intel is going to dynamic thread splitting...

Why the term "rentable unit" for it, though?

Running speculative thread on E-core would not benefit anything. Speculative thread needs to be run ahead of main thread - so it need to be faster than main thread and so close to main thread that it will be part of cpu core to offer any meaningful help to execution.

Intel 17th Gen CPUs to Get Rentable Units: Why Hyper-Threading is Going Away | Hardware Times

Intel’s adoption of the hybrid core architecture has significantly changed the roadmap of the PC chipmaking industry. More and more applications are now taking advantage of the “secondary” low-power E-cores to boost performance and efficiency. This approach has its shortcomings, which Intel...www.hardwaretimes.com

Intel is going to dynamic thread splitting...

I guess that the Slipstreame 2.0 will come, because E-core is best choice for speculative precomputation.

SiliconFly

Golden Member

At least I was spot on about this a while back... 🙂My bad. I think i didn't explain myself clearly.

(I was just comparing Zen 4 -> Zen 5 vs RPL -> ARL. Thats all)

What I was trying to say was, AMD is going from Zen 4 to Zen 5 (say N4 to N4P), and the density increase is non-existent. So, the transistor budget remains the same. The only way to increase IPC is to re-architect with the same amount of transistors (assuming the die size remains the same).

And Intel is going from RPL to ARL (say Intel 7 to 20A), the density increase is from 100 MTr/mm2 to around 300+ MTr/mm2. ARL gets 3X the transistors for the same die area.

Intel can shrink the ARL die to save cost, but I don't think they'll do that. I think the ARL die is gonna get a significantly higher transistor budget compared to RPL, And those excess transistors can easily be used to increase L2/L3 caches in the cpu tile or even increase core logic for more performance.

I did say ARL is gonna get a bigger cache. News leaks suggest that ARL is getting a 50% bump in L2. i.e, up to 3MB of L2.

Looks like, instead of doing something great with the massive transistor budget, Intel has chosen the easiest & safest way instead. Yuck.

Last edited:

igor_kavinski

Lifer

Yeah coz that will mainly translate to better gaming performance and that's what they prefer to focus on. They have been failing at competing in MT workloads for a while now (barely stand up to 5950X and 7950X).Looks like, instead of doing something great with the massive transistor budget, Intel has chosen the easiest & safest way instead. Yuck.

Leak was talking about L2 not L3.I did say ARL is gonna get a bigger cache. News leaks suggest that ARL is getting a 50% bump in L3. i.e, up to 3MB of L3.

Why can't it be both?Looks like, instead of doing something great with the massive transistor budget, Intel has chosen the easiest & safest way instead. Yuck.

Eh. Doubt they 'prefer' to focus on gaming performance.Yeah coz that will mainly translate to better gaming performance and that's what they prefer to focus on.

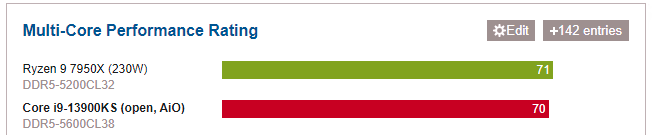

?They have been failing at competing in MT workloads for a while now (barely stand up to 5950X and 7950X).

igor_kavinski

Lifer

Intel Core i9-13900KS mit 6,0 GHz im Test

Der Core i9-13900KS ist der erste Intel-Prozessor mit bis zu 6,0 GHz ab Werk. Die dritte Special Edition in Anwendungen und Spielen im Test.

Even their KS paired with faster memory has trouble matching a 7950X in overall MT perf.

SiliconFly

Golden Member

Oops. fixedLeak was talking about L2 not L3.

SiliconFly

Golden Member

Definitely has a positive effect on gaming. But otherwise,.. meh.Yeah coz that will mainly translate to better gaming performance and that's what they prefer to focus on. They have been failing at competing in MT workloads for a while now (barely stand up to 5950X and 7950X).

SiliconFly

Golden Member

I don't think it can be. Some leaks suggest ARL has RWC+ cores. Others suggest it has the first iteration of the LNC cores (and hence no hyper-threading).Why can't it be both?

If ARL has RWC+ cores, then there's nothing new to expect, except bigger caches and some minor improvements I guess.

If it has some form of LNC, then it's a whole different story. Need more clarity about ARL cores though.

The benchmark you linked shows a single percentage point difference. I wouldn't consider that having trouble matching 7950X MT performance.

Intel Core i9-13900KS mit 6,0 GHz im Test

Der Core i9-13900KS ist der erste Intel-Prozessor mit bis zu 6,0 GHz ab Werk. Die dritte Special Edition in Anwendungen und Spielen im Test.www-computerbase-de.translate.goog

View attachment 84509

Even their KS paired with faster memory has trouble matching a 7950X in overall MT perf.

Just to save us time... Yes - I know it isn't anywhere near as efficient.

LolI don't think it can be. Some leaks suggest ARL has RWC+ cores.

No. Only person who thinks it's RWC+ is witeken...Need more clarity about ARL cores though.

igor_kavinski

Lifer

From what I understand, Intel will slice a single thread into different instruction streams and try to process them on different cores so that if one instruction stream comes to a halt for whatever reason, the processing keeps going on, on the other cores and results are ready before the execution reaches that part of the process's instructions.Isn't he the hardcore intel apologist? can someone explain rentable cores to me.

igor_kavinski

Lifer

You are ignoring the fact that it takes a lot more effort to prevent the 13900KS from throttling. Similarly, the 5950X trumps the 12900KS.The benchmark you linked shows a single percentage point difference. I wouldn't consider that having trouble matching 7950X MT performance.

Saylick

Diamond Member

That makes sense on paper but I'm not sure that's how it works in real life. I'm just an arm chair CPU architect, but if a single thread could be simply chopped up into smaller, bite sized portions that can be executed in parallel, wouldn't a GPU be better at the task? Single threaded processes tend to have a crap load of dependencies, which is why they run best on CPUs to begin with. If portions of the instruction stream could be done in parallel, well that's where having a superscaler execution engine comes in.From what I understand, Intel will slice a single thread into different instruction streams and try to process them on different cores so that if one instruction stream comes to a halt for whatever reason, the processing keeps going on, on the other cores and results are ready before the execution reaches that part of the process's instructions.

igor_kavinski

Lifer

You would need a GPU that understood x86, AKA LARRABEE! 😀That makes sense on paper but I'm not sure that's how it works in real life. I'm just an arm chair CPU architect, but if a single thread could be simply chopped up into smaller, bite sized portions that can be executed in parallel, wouldn't a GPU be better at the task?

From what I understand, Intel will slice a single thread into different instruction streams and try to process them on different cores so that if one instruction stream comes to a halt for whatever reason, the processing keeps going on, on the other cores and results are ready before the execution reaches that part of the process's instructions.

Isnt it what a OoO uarch is supposed to do..?.

very similar to how download streams work. each connection within the main download will download a portion of the file, if one fails others take over and then decompress the download from cache.From what I understand, Intel will slice a single thread into different instruction streams and try to process them on different cores so that if one instruction stream comes to a halt for whatever reason, the processing keeps going on, on the other cores and results are ready before the execution reaches that part of the process's instructions.

this being intel and I need not explain some half baked ideas they've had. I'm not sure if it'll work out well or bad.

igor_kavinski

Lifer

That happens inside a single core. Rentable cores are supposedly going to take this a step further and allow the instructions of a single thread to be executed out of order on different cores.Isnt it what a OoO uarch is supposed to do..?.

igor_kavinski

Lifer

I can believe it if Intel Israel is behind this innovation. They seem to be the ones always rescuing Intel in their time of need.this being intel and I need not explain some half baked ideas they've had. I'm not sure if it'll work out well or bad.

TRENDING THREADS

-

Discussion Zen 5 Speculation (EPYC Turin and Strix Point/Granite Ridge - Ryzen 9000)

- Started by DisEnchantment

- Replies: 25K

-

Discussion Intel Meteor, Arrow, Lunar & Panther Lakes + WCL Discussion Threads

- Started by Tigerick

- Replies: 25K

-

Discussion Intel current and future Lakes & Rapids thread

- Started by TheF34RChannel

- Replies: 24K

-

-