Saylick

Diamond Member

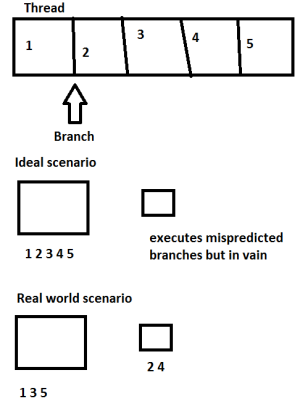

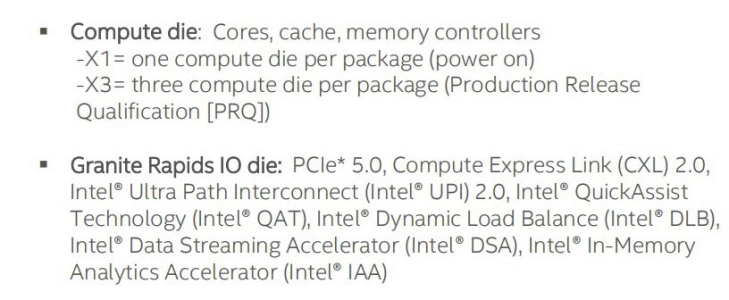

But why do that if the same core has enough width in the execution engine to do it in parallel and "in-house"? That's what superscaler execution is all about. If a single thread can't saturate the execution engine, then you can use SMT to bring in another thread.That happens inside a single core. Rentable cores are supposedly going to take this a step further and allow the instructions of a single thread to be executed out of order on different cores.

If there truly is a thread that has a portion that is so embarrassingly parallel that bringing in another core to do the work benefits it, a GPU likely would be a better choice. In reality, I don't think there's too many programs that fall in this Goldilocks region where it runs best on what would effectively be a 20+ wide execution engine (made from two or more smaller CPU cores) but not so embarrassingly parallel that a GPU could run it faster.