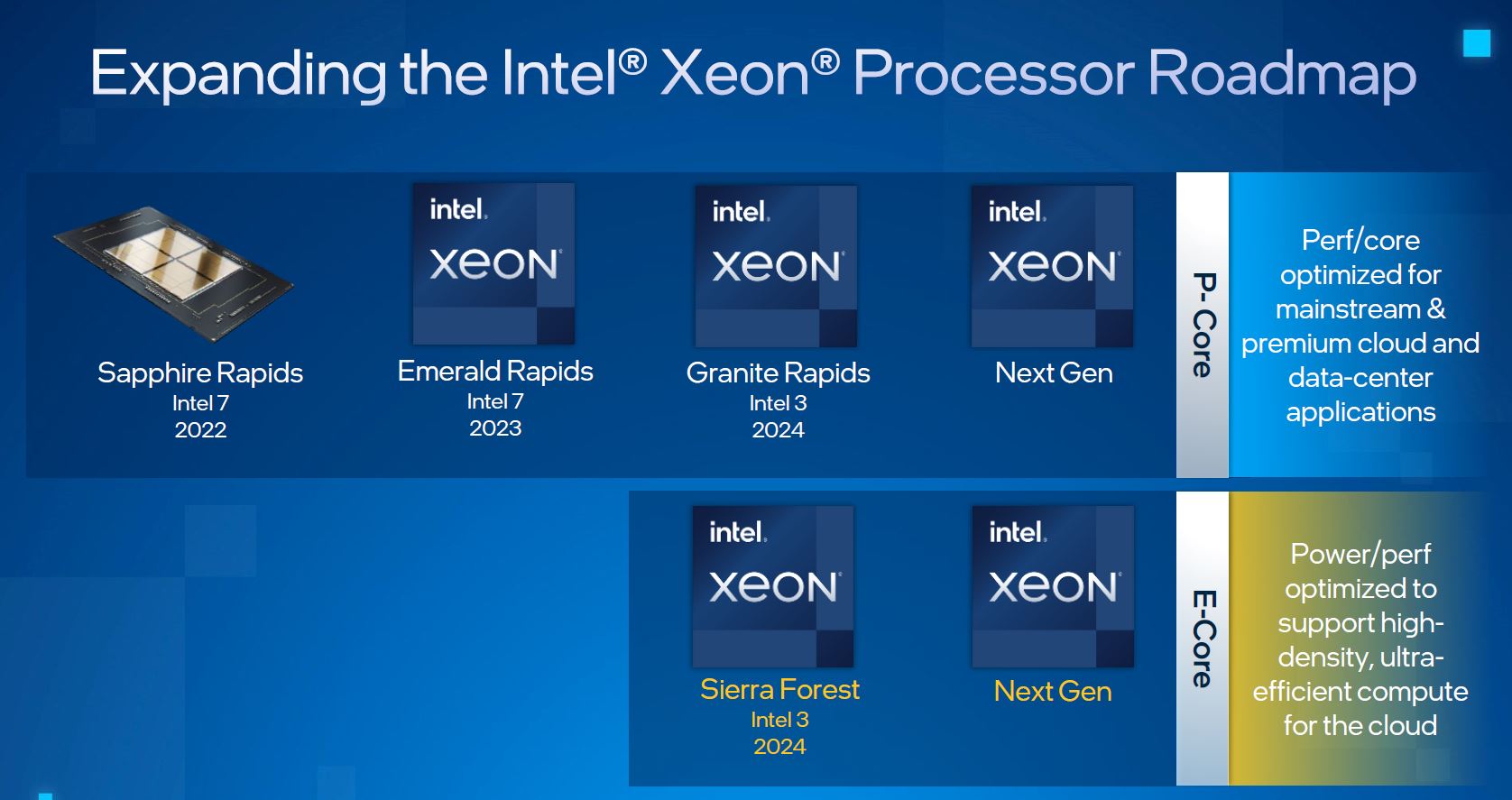

I don't think it'll quadruple Granite Rapids core count. It might double it at best for lower cost and better power efficiency for cloud workloads.

We know that Granite Rapids and Sierra Forest are on the same platform and that they are disaggregated. The platform capabilities will be derived from the base Foveros tiles. To be competitive, it will be a “4-stack” Foveros design, which will allow for a large “Rambo” cache as well. Each of the top 4 tiles (or groups of subtiles) will be approx 500 mm2. Lets assume 20% of this area will be lost to Foveros power delivery and tile interconnect. One important thing to keep in mind is that these will be made on Intel 3, so we will get 1.5x or so density improvement wrt Intel 7.

Granite Rapids: So how many P-cores can one fit in 600mm2 (400x1.5) on Intel 7? 15 Golden cores take 200mm2, or 13.3mm2 per core. Lets make the new core size 15mm2 to account for new features. The answer is 40 P-cores per tile, or 160 cores per chip with 4 top tiles. I watered down this number to 128. Of course power will be a big gating factor. The TDP of these chips might top 500/600W.

Sierra Forest: Assuming 3 E-cores per P-core, we get 384 max E-cores. This number could be higher, even as high as 512, if a denser and more power efficient version of the Intel 3 process is used instead.

Now, how these tiles are packaged in SKUs is of course a business decision based on customer needs, competitive landscape, and yields. Unlike Sapphire Rapids, there is no longer a need to always include 4 tiles to get the full platform capability. Using just 2 E-core tiles might reach close to 256 cores, arriving at your likely configuration. The beautiful thing is that these are

late binding decisions, that rely solely on backend packaging processes.

Falcon Shores features "anstrom era process", so 20A is a good expectation.

The base tiles that have all the I/O may stay with Intel 3; Intel 20A may again be just like Intel 4, and only have high performance libraries. Subtiles of the Xe tile maybe made with 20A and external sources. The x86 core tiles will likely stay as-is on Intel 3 for the first Falcon Shores release. The next Falcon Ridge release could be based on Diamond Rapids and whatever the next E+core is. Once there is a stable platform with well defined chiplet interfaces, there is a lot of flexibility.