Ask yourself this, do companies have a 20+ year track record of technical measurements suddenly change things? Does it signal anything to you if they do so when things appear to be going horribly wrong, product delayed 2+ years and so on? Do you find comfort in this new technical measurement showing that instead of the hard data showing things well off the rails which is no longer disclosed for some reason, instead it shows a major technological leap forward? Even if if completely contradicts the basic foundation of the company’s financial basis, essentially that shrinks lower cost and add performance? See why we were laughing so hard?

Track Records Like Clockwork:

If you recall the first Intel 32nm parts, Arrandale (Westmere), were released in January of 2010. As per the Tick-Tock architecture plan there should have been a new architecture in January of 2011 and a shrink of that architecture in January of 2012. Sandy Bridge, the 32nm new architecture came out on time, as did the Ivy Bridge shrink. All is good so far.

Haswell was the new architecture on 22nm and, well, it wasn’t exactly on time, ~6 months late with a June 2013 release. We won’t get into the weeds discussing the long tails of older processes but the short version is that 22nm yields were still so low at this point that Intel was heavily pushing 32nm parts to OEMs and APAC countries to keep margins up. The normal swift cutover of sales from an old process to a new wasn’t publicly messaged this time around and Intel hasn’t talked about it since. For some reason SemiAccurate does not find this curious.

If you go to China and look at what the white box vendors sell, you will see they are still doing quite a brisk business in Haswell (22nm) CPUs, new ones. Not sure what this implies since it contradicts the official messaging about how Intel makes money, but feel free to do the research yourself. Officially those chips are vastly more expensive to make than the 14nm equivalents but they must be coming from somewhere, right? And who knows why Intel would do this in light of the official cost structure messaging.

The shrink to 14nm was heralded by Broadwell which officially came out in September of 2014, again an ~15 month release or another ~3 month delay. Intel claimed, correctly, that 14nm shipped for revenue in 2014 as promised. If you were cynical you would point out two things. First Intel shipped only the lowest volume, 2C GT1/2, lowest power parts in quantities that meant no one could realistically make products with them. Secondly you might consider that one SemiAccurate mole pointed out that Intel management pays bonuses based on when certain products and processes ship. 14nm shipped ‘on time’ by that metric, but we aren’t that cynical.

The usable 14nm parts shipped in January of 2015 or ~18 months after Broadwell actually came out. If you take the first September 2014 date, the shift from 22nm to 14nm took 2.25 years, 2.5 years if you take the real date into account. In any case it was a slip, Tick-Tock was a year off by this point and slipping. If you don’t think so, look at Skylake, the 14nm new architecture, it shipped in September of 2015 or ~9 months after Broadwell. Was it early or was it on time and Broadwell was late? Your call.

The Rails Are Over There:

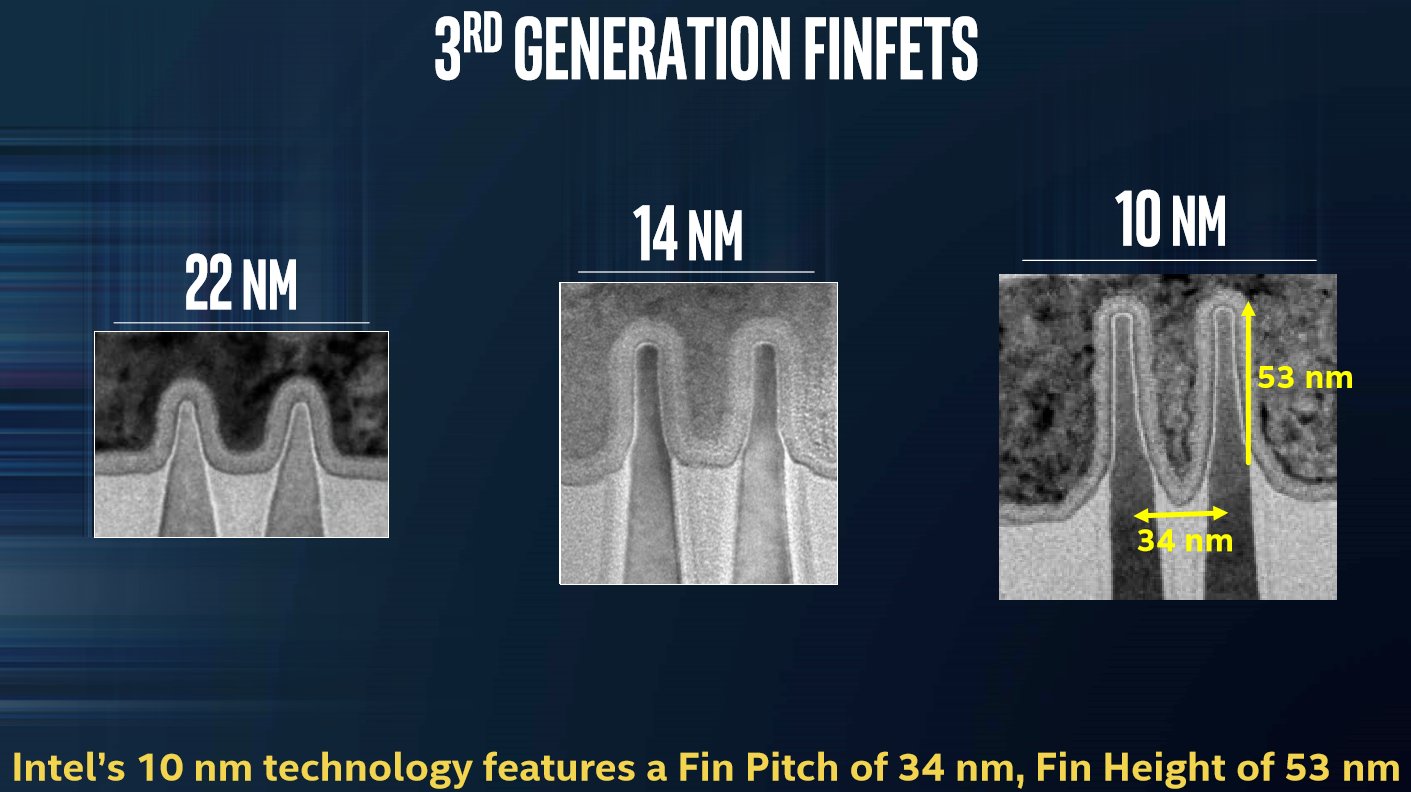

Now if you look at Intel roadmaps of yore, the cadence should have gone 32nm (Westmere/Arrandale) in 2010, Sandy Bridge in 2011, Ivy Brige in 2012, Haswell in 2013, Broadwell in 2014, Sky Lake in 2015, Cannon Lake (10nm) in January 2016, Icelake (10nm) in January of 2017, and Tigerlake/Firelake (7nm) at CES in about 2 weeks aka January 2018. Instead there were the slips described above and Cannon, due ~2 years ago, isn’t out. Instead we have multiple “new architectures” that seem to pop up on the Intel roadmaps as soon as OEMs need to start production on the 10nm parts that were previously there.

The first of these was Kaby Lake which

we exclusively told you popped up in May of 2015. It was a rename with a minor uncore change or two which is now a ‘new architecture’ and ‘new generation of Core’ in Intel parlance. 10nm Cannon was pushed out a year. When it came time for Cannon to ship after Kaby, yes you guessed it,

Coffee Lake popped up on the roadmaps. Still 14nm.

That was a year ago and Cannon on 10nm was definitely going to ship in late 2017 or early 2018. Which meant, wait for it, when that time rolled around we get… 14nm Whiskey Lake, another ‘new architecture’ and ‘new generation of Core’! Be still my beating heart. Rumors about a 14nm part after Whiskey are making the rounds now too.

One aside to think about, Intel’s official claims versus reality. Officially these 14nm products are on 14+, 14++, and 14+++ processes which are, again officially, big steps forward. SemiAccurate

went into great detail about why this wasn’t true earlier, these are just the standard mid-life PDK updates that bring minor benefits, mostly from a relayout of the chip, not the process. It was about this time that Intel changed policy and refused to give out transistor counts and die sizes, even on released products. Why? What do you think that data would show about Skylake, Kaby Lake, Coffee Lake, and soon Whiskey Lake? Do you think it would show massive area gains that the company claims the +/++/+++ processes bring?

All isn’t lost however, 10nm is now set for late 2018, officially, and that is where things really begin. Subscribers with weak hearts please stop reading here, if you think the 2+ year delay on 10nm is bad or believe Intel’s Hyperscaling distractions, this next bit won’t be of much comfort.

Note: The following is for professional and student level subscribers.

Disclosures: Charlie Demerjian and Stone Arch Networking Services, Inc. have no consulting relationships, investment relationships, or hold any investment positions with any of the companies mentioned in this report.