Look, the Athlon 300U and Ryzen 3200U already more than doubles passmark score of the A6-9220/9225 at the same TDP, there is really NO WAY, and even if there was it is better to re-use picasso than putting money on another product.

They need to double the cores while maintining clocks and tdp in order to more or less match 2C/4T Picasso MT at the same TDP. And Picasso is already running on a old node by now. That just pointless.

Ryzen 3200u(Q2 2019)/(2.6 to 3.5) =

nT:4937

1T:1740

A9-9425(Q2 2018)/(3.1 GHz to 3.7 GHz) =

nT:2533

1T:1497

A9-9420e(Q2 2018)/(1.8 GHz to 2.6 GHz) =

nT: 1904

1T: 1124

A near 1 GHz increase lead to an average between 60 samples and 22 samples from 1124 to 1497 is 373 pts.

If AMD added 1 GHz again, and had a similar change between Steamroller(13T/28nm) to Excavator(9T/28nm). We can simply add the 373 pts to the A9-9425, which will come out to 1870 pts. However, the biggest opportunity for AMD is not a revision of 15h, but a new architecture.

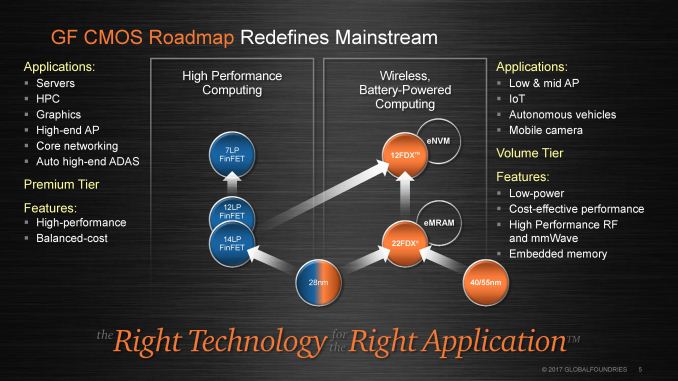

Certain designs can get a full-esque shrink from 9T-28nm to 8T-22nm. If we assume there is a shrink as the FPU scheduler/FMAC shrunk 38%/35% from 13T/28 to 9T/28. Another shrink, up to 40% would allow for certain special things to happen to the FMACs. The only other numbers were of the I-cache control/35% shrink, if a 15h revision it could probably allow for 128 KB L1i on 22FDX. The only reason to go that route is to replace Zen, which shouldn't be the purpose of 22FDX/12FDX.

It is better to have something like the below, than a continuation of 15h.

32 KB L1i 10T/2 x 16KB L1d 10T/512KB L2 10T/8T <== 10T for short channel effect immunity, reduced delay, reduced power consumption, reduced area, etc.

3 ALU/3 AGU with a new scheduler, distributed physical register file <== slightly more IPC, the dPRF should reduced delay by 10%? and power by 20%? and area 40%.

FPU could do split with each core gets 2x FADD+2x FMUL or 4x 128b FMAC in a single unit. The removal of the MMX is key, to the potential focus towards mixed-point calculations. At least, half of the FPU will be fixed point and the other half floating point. With enhancements towards fixed + floating calculations and fixed <-> floating conversions. With bfloat on the floating side and integer mantissas + float exponent on fixed point side.

Pure FMAC/Single Unit = Highest efficiency // Best option. <-- this would boost it on 1T.

FMUL+FADD/Two unit = Highest speed // Second best option. <-- this would boost it on nT.

There is also mixed track height; 8T/22nm for critical paths with LVT, 7T/22nm for non-critical paths RVT/HVT. Which can further improve density and power, while negligible to no performance loss. There is definitely enough extremely modern optimizations that can be done to allow higher IPC and higher frequency. While reducing area utilization and power consumption. This all on a node that is similar in price to current gen 28nm, and lower development costs than 14nm onwards.