Verano is a village with barely 1000 inhabitants, i doubt that it was ever mentioned elsewhere than in this thread, they just made a typo out of Verona since that s a big city that is close to Venice.Well, why wouldn't AMD use the Verano name for new EPYC series or why would that be a mistake?If that city didn't exist, it would be quite logical to assess it as a mistake in marketing presentation. So you have two cities Verona and Verano, so now we can have a beer in Verano.

-

We’re currently investigating an issue related to the forum theme and styling that is impacting page layout and visual formatting. The problem has been identified, and we are actively working on a resolution. There is no impact to user data or functionality, this is strictly a front-end display issue. We’ll post an update once the fix has been deployed. Thanks for your patience while we get this sorted.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Discussion Zen 7 speculation thread

Page 5 - Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.

- Status

- Not open for further replies.

Yes, that 40% IPC bubble is Zen 5's trademark.Regarding Zen5, people have blown their own bubble based on the Epyc (Zen5) results.

Yes, but... reading the Chips'n'Cheese profiled data, majority of stalls within the Zen 5 core are caused by the frontend latency.Zen5 is a massively, but cautiously, expanded (widened and deepened) x86 core. It features a super-advanced BPU and prefetching. It's very extensive and significantly deeper than previous Zen generations. The BPU in Zen5 anticipates two consecutive branches and can have three branch windows. Zen5 sees very long and complex branch patterns.

This metric is hugely flawed. Capacitance/frequency optimization, weird IO stuff, niche features, etc. Specifically, Zen 5 invested a notable amount of transistors to support the AVX-512 full-speed data flow.Zen5 has about 26% more transistors per core, or 218 million more than Zen4. The difference is practically the entire Skylake+L2 core (217 million transistors).

Even that 13% is not so impressive for such ambitious design, right? I know the relative base value of Zen 4 was higher than Zen 1's but still - there are Apple and Qualcomm.The IPC increase is an average of +16% (average +13% Int and average +24% FP).

Compared to Zen2, it's about 50-55% (average IPC increase).

Those sizes are cool, but how about the int RF or ROB size?

At 448 slots Zen 5's ROB is still smaller than Golden Cove's 512, let alone Lion Cove's 576.

The same applies to 240 int RF vs 280-300 of Intel's.

Both limits manifest themselves in the profiled data.

fastandfurious6

Banned

Zen 5 invested a notable amount of transistors to support the AVX-512 full-speed data flow.

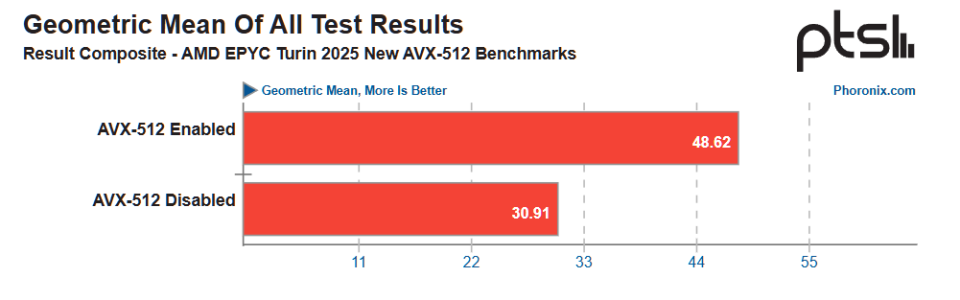

the results:

this stuff sells..... decision makers see big number and make decision.....

Even that +13% ipc is not so impressive for such ambitious design, right?

zen6 gonna fix all quirks and latency..... zen5 got rushed

Well, it surely sells to AVX-512 shops. Like AMX sells to whatever AI shops.this stuff sells..... decision makers see big number and make decision...

fastandfurious6

Banned

cloud providers........ gazillions of orders

It's not something AMD exclusive unlike Client CPUscloud providers........ gazillions of orders

There's very rarely any official data for anything like this.Until official data for the Zen5+L2 core is available, this is the only way.

Using area is a much better metric IMO.

marees

Platinum Member

It is zen6+ (despite the misleading site name, Charlie is usually accurate)The server CPU codename Verano is neither a typo, nor is it a reference to Vöran in South Tyrol. Rather, it refers to Veràn in Lombardy, right outside of Milan. AMD chose this name because this CPU isn't Zen 7 but a Zen 3 refresh. ;-)

Update June 16, 2025 @ 945am: Well we screwed this up, and we blame chronic lack of sleep last week coupled to ultra-short time lines to write up the info. Verano is _NOT_ the successor to Venice, it is a Venice variant. Florence is Venice+1, something we knew and should have remembered before writing the above paragraph.

AMD Lays Out their MI350, MI400, and MI500 Roadmap

At AMD’s Advancing AI event, they laid out the roadmap for future AI GPUs and racks.

www.semiaccurate.com

www.semiaccurate.com

Asterox

Golden Member

If you look at the classic Geekbench test, you get a much broader picture. Roughly speaking, Zen 5 brings an average of 100% better singlecore and multithread CPU score.Compared to Zen2, it's about 50-55% (average IPC increase).

Zen5 has the most powerful and modern BPU in the x86 architecture.

Golden/RaptorCove

BTB L0 128

BTB L1 5K

BTB L2 12K

Return Address Stack 2-4

LionCove

BTB L0 256

BTB L1 6K

BTB L2 12K

Return Address Stack 24

Zen4

BTB L0 128

BTB L1 1.5K

BTB L2 7K

Return Address Stack 32

Zen5

BTB L0 1K!(1024!)

BTB L1 16K!

BTB L2 8K(victim cache for BTB L1)

Return Address Stack 52x2(104 for SMT)

Golden/RaptorCove

Cache L3 ST 90-100GB/s (60-70 cycles)

LionCove

Cache L3 ST 57GB/s (84 cycles)???

Zen5

Cache L3 ST 173GB/s (48 cycles)!!!

Edit:

The Zen5 BPU can predict the next two independent branch paths not only for two threads(SMT) but also within a single thread(ST). When the ST code is heavily branched, the second decoder cluster can take over part of the ST code (2x4-Wide(8-Wide))! (Zen1-Zen4 decode 4-Wide)

SMT Zen4 profit average +13%

SMT Zen5 profit average +18%

OP cache 6144 (instruction fusion) 16-way, 12 ops/ST cycle and 2x 6ops/SMT cycle. Thanks to instruction fusion, the Zen5 op cache has larger capacity than the Zen4 (6912, 12-Way, 9 ops/cycle) op cache.

If you take average numbers, that would roughly be the comparison.

If all the L3 is placed outside the die using vCache, I would definitely expect AMD to raise core counts for Zen 7. In fact, I would think double.... or as many as they could feed with bandwidth and the power of their socket limitation at the time.MLID shows very modest increase of core count from Zen 6c -> Zen 7c being 32 -> 33 per CCD. But freeing up a lot of die space by moving all of L3 to V-Cache, and increasing the transistor budget that way (in addition to transistor density from new node).

MLID also mentioned L2 going from 1 MB to 2 MB which should only have a modest transistor count and die area increase.

I wouldn't be surprised if both AMD and Intel start producing new designs ONLY ever 2 nodes. They might just do a "refresh" every half node (or quarter node 😉). It doesn't make sense to redesign without an increase in transistor budget IMO.Where have you been? Every node is a half node now...quarter node really.

If that is the case, then Zen 6 could show some interesting IPC improvements by freeing this up and having a lower latency IOD as well.Yes, but... reading the Chips'n'Cheese profiled data, majority of stalls within the Zen 5 core are caused by the frontend latency.

... and lots of applications today in DC can take advantage of AVX512... so it isn't just marketing, it really makes a difference.this stuff sells..... decision makers see big number and make decision.....

Well then .... that makes a great deal of sense. I definitely can't see Zen 7 before 2028 .... maybe 2029 unfortunately.Update June 16, 2025 @ 945am: Well we screwed this up, and we blame chronic lack of sleep last week coupled to ultra-short time lines to write up the info. Verano is _NOT_ the successor to Venice, it is a Venice variant. Florence is Venice+1, something we knew and should have remembered before writing the above paragraph.

Well then .... that makes a great deal of sense. I definitely can't see Zen 7 before 2028 .... maybe 2029 unfortunately.

While Lisa Su said (at recent AI summit) that some new AI tools will allow AMD faster release schedule, you expect a slow down, Zen 7 taking 50% longer than any other Zen releases.

What are your reasons for this? Why do you think you have a better idea about AMD release schedule than Lisa?

fastandfurious6

Banned

Lisa Su said (at recent AI summit) that some new AI tools will allow AMD faster release schedule

exactly!!!! said that few weeks ago and everyone here was like "but we don't know, AMD doesn't confirm anything" lol

everyone uses AI for both r&d and development lmao, it's a pure accelerator no frills just works. only needs pair of senior eyes and strong QA/testing (also enhanced by AI) to detect the unavoidable hallucinations

The second decode cluster is only when SMT is active it doesn't work in ST. C&C even postulates it is essentially a return of clustered multi-threading in Bulldozer.Edit:

The Zen5 BPU can predict the next two independent branch paths not only for two threads(SMT) but also within a single thread(ST). When the ST code is heavily branched, the second decoder cluster can take over part of the ST code (2x4-Wide(8-Wide))! (Zen1-Zen4 decode 4-Wide)

Most of the gains are due to the new ISA, not the 512-bit path.

Without the 512-bit but keeping the 256-bit path you get +29%.When taking the geometric mean of all the raw AVX-512 performance benchmarks, AVX-512 in the default FP512 configuration yielded 1.45x the performance compared to disabling AVX-512 outright. Having the 512-bit data path allowed for 1.12x the performance compared to running the EPYC 9755 processor in the 256-bit data path mode, similar to how AVX-512 operates with Zen 4.

For power/area efficiency it makes sense to have AVX512-256.

Last edited:

exactly!!!! said that few weeks ago and everyone here was like "but we don't know, AMD doesn't confirm anything" lol

everyone uses AI for both r&d and development lmao, it's a pure accelerator no frills just works. only needs pair of senior eyes and strong QA/testing (also enhanced by AI) to detect the unavoidable hallucinations

Exactly. When I posted this in another thread (with link to the video where Lisa said it) someone replied that AMD will only do it for datacenter GPUs.

Which makes zero sense. If you develop tools to accelerate your work, you will deploy the same tools across all the divisions, across the product stack.

And for AMD, which has such a wide portfolio of products, AMD can get the best return on the investment into these tools.

And you don't need "heavy branching" to make clustered decode work. Branching happens quite often enough that Tremont reaches 6-wide quite often even without the load balancer.The second decode cluster is only when SMT is active it doesn't work in ST. C&C even postulates it is essentially a return of clustered multi-threading in Bulldozer.

gdansk

Diamond Member

Not what I said at all. If you'd like to be charitable go read it again. But to reiterate:Which makes zero sense. If you develop tools to accelerate your work, you will deploy the same tools across all the divisions, across the product stack.

1. ML has been used in hardware design for sometime. Cadences didn't improve instead have become worse. Why?

2. Design complexity grows. Often beyond any increase in productivity.

3. MI is getting more resources. It should have more overlapping work and could have a shorter cadence.

And obviously the Zen teams are doing far more work on producing variants and proliferation of SKUs into more niches than they were before. I don't expect the cadence to improve.

Last edited:

I always felt like AMD saw potential vulnerabilities in Zen5's design in the later engineering stages causing them to preemptively disable parts of the silicon to prevent exploitation.Even that 13% is not so impressive for such ambitious design, right?

gdansk

Diamond Member

No, it's pretty good. People are just expecting too much exploitable ILP. Despite all the changes Zen is still limited by the frontend and it is (allegedly) the most difficult part of an x86 chip.Even that 13% is not so impressive for such ambitious design, right?

Last edited:

I just don't think that AMD hit their goals they were expecting too tbh.I always felt like AMD saw potential vulnerabilities in Zen5's design in the later engineering stages causing them to preemptively disable parts of the silicon to prevent exploitation.

TBF, Zen 5's tock just does not seem great. Esp in comparison to Zen 3.No, it's pretty good. People are just expecting way too much ILP from existing real world x86 code.

gdansk

Diamond Member

That's how fruit are picked.TBF, Zen 5's tock just does not seem great. Esp in comparison to Zen 3.

LNC wasn't a bad tock either. That's just how fruit are picked.That's how fruit are picked.

itsmydamnation

Diamond Member

I just don't think that AMD hit their goals they were expecting too tbh.

TBF, Zen 5's tock just does not seem great. Esp in comparison to Zen 3.

Zen5 is very different/odd compared to everyone else.LNC wasn't a bad tock either. That's just how fruit are picked.

They went and built way bigger bones but then kept the muscle at zen4+ size.

if i remember it was supposed to be on 3N , so it ended up being a bigger sized core on 4N.

it seems the balance mantra is still king and they aren't in a rush to take all the sugar many other cores have ( ROB/reg file size ).

im guessing they would have targeted higher clocks on 4N and some larger internal structures and then Zen5 would have been more inline with typical.

here is hoping for Zen6 to spend 2 gens of sugar at once + good clock boost to boot.

if i was a betting man Zen 7's probably gonna but Zen5 plus a bit style up lift.

- Status

- Not open for further replies.

TRENDING THREADS

-

Discussion Zen 5 Speculation (EPYC Turin and Strix Point/Granite Ridge - Ryzen 9000)

- Started by DisEnchantment

- Replies: 25K

-

Discussion Intel Meteor, Arrow, Lunar & Panther Lakes + WCL Discussion Threads

- Started by Tigerick

- Replies: 24K

-

Discussion Intel current and future Lakes & Rapids thread

- Started by TheF34RChannel

- Replies: 24K

-

-