-

We’re currently investigating an issue related to the forum theme and styling that is impacting page layout and visual formatting. The problem has been identified, and we are actively working on a resolution. There is no impact to user data or functionality, this is strictly a front-end display issue. We’ll post an update once the fix has been deployed. Thanks for your patience while we get this sorted.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Question Zen 6 Speculation Thread

Page 365 - Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.

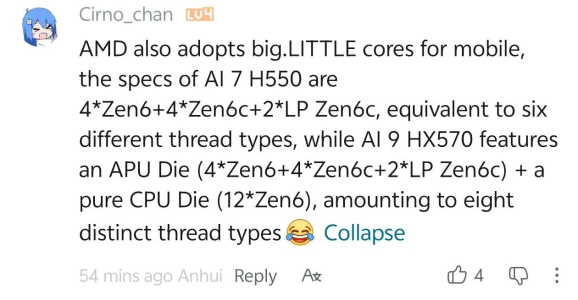

Potential config for the Medusa Point line up.

Doesnt seems like what we know/heard so far?

View attachment 138314

That's what MLID leaked some time ago. Like a year ago.

MerryCherry

Member

Windows scheduler is going to have a stroke.Potential config for the Medusa Point line up.

Doesnt seems like what we know/heard so far?

View attachment 138314

Markfw

Moderator Emeritus, Elite Member

That not big.little the way Intel does it. Zen6c is just s little less cache, the core otherwise is the same.Potential config for the Medusa Point line up.

Doesnt seems like what we know/heard so far?

View attachment 138314

adroc_thurston

Diamond Member

True ISA-wise, but from the sched POV freq delta puts them into way different perf tiers.That not big.little the way Intel does it. Zen6c is just s little less cache, the core otherwise is the same.

Markfw

Moderator Emeritus, Elite Member

But capability is the same. for example when Intel started this avx-512 was in big, but not little. The current titles are the same in general, the capability is not there is the little for some features.True ISA-wise, but from the sched POV freq delta puts them into way different perf tiers.

edit: so the same code can run on any core, just runs slower on c core threads.

Covfefe

Member

All of the cores in a big.LITTLE CPU have to support the same ISA. There's never a case where some code can run on one core but not another.But capability is the same. for example when Intel started this avx-512 was in big, but not little. The current titles are the same in general, the capability is not there is the little for some features.

edit: so the same code can run on any core, just runs slower on c core threads.

All of the cores in a big.LITTLE CPU have to support the same ISA. There's never a case where some code can run on one core but not another.

They don't HAVE to. For example if you wanted to make a core without AVX512 or heck if you really want to get crazy without any SIMD/FP at all you could do it. Just have it trap when an instruction it doesn't support is encountered and reschedule it on a core that do support it (plus set a flag in the scheduler to insure it that process doesn't ever get scheduled on the cut down core ever again)

Not saying it really makes sense to do this today (because the "gain" from a stripped down core in terms of area/power/performance isn't worth providing enough SIMD/FP free work for it) but the one constant in the computing world is that things change so never say never. Maybe someday we can make photonic processors that run an order of magnitude faster than current technology but our "transistor equivalent" budget is multiple orders of magnitude less so we have to pick and choose what it supports.

Covfefe

Member

Interesting, do you have any examples of CPUs that work this way?They don't HAVE to. For example if you wanted to make a core without AVX512 or heck if you really want to get crazy without any SIMD/FP at all you could do it. Just have it trap when an instruction it doesn't support is encountered and reschedule it on a core that do support it (plus set a flag in the scheduler to insure it that process doesn't ever get scheduled on the cut down core ever again)

Not saying it really makes sense to do this today (because the "gain" from a stripped down core in terms of area/power/performance isn't worth providing enough SIMD/FP free work for it) but the one constant in the computing world is that things change so never say never. Maybe someday we can make photonic processors that run an order of magnitude faster than current technology but our "transistor equivalent" budget is multiple orders of magnitude less so we have to pick and choose what it supports.

itsmydamnation

Diamond Member

None I Know of, amd have multiple patients for it.Interesting, do you have any examples of CPUs that work this way?

Interesting, do you have any examples of CPUs that work this way?

Didn't Intel had a CPU generation where they had big cores that were designed to support AVX512 and little cores that weren't, and they ended up shipping it with AVX512 disabled in the big cores? So they might have experimented with it and decided it wasn't worth the trouble, or maybe Microsoft told them to pound sand when they said they wanted this kind of thing in the Windows Scheduler so they had no choice.

biostud

Lifer

Yeah, and if you disabled the little cores you could activate AVX512 on the big cores IIRC.Didn't Intel had a CPU generation where they had big cores that were designed to support AVX512 and little cores that weren't, and they ended up shipping it with AVX512 disabled in the big cores? So they might have experimented with it and decided it wasn't worth the trouble, or maybe Microsoft told them to pound sand when they said they wanted this kind of thing in the Windows Scheduler so they had no choice.

Thunder 57

Diamond Member

Didn't Intel had a CPU generation where they had big cores that were designed to support AVX512 and little cores that weren't, and they ended up shipping it with AVX512 disabled in the big cores? So they might have experimented with it and decided it wasn't worth the trouble, or maybe Microsoft told them to pound sand when they said they wanted this kind of thing in the Windows Scheduler so they had no choice.

Yeah, and if you disabled the little cores you could activate AVX512 on the big cores IIRC.

The original Alder Lake worked this way.

Markfw

Moderator Emeritus, Elite Member

Yes, and I had one. I think it was a 12700k, but correct me if I am wrong on the model number. and I did disable the little cores and ran a avx-512 app and it started taking 300 watts ! (per my kill-a-watt)The original Alder Lake worked this way.

LightningZ71

Platinum Member

Familiar, yes. The difference being that server applications run at significantly lower frequencies with far more manageable hot spots as a result. The thermal load from, for example, Nova lake's P core running at 6+Ghz is going to be savagely harder to deal with than a 64 core title running at sub 5Ghz. I'm sure that there is a solution, but is it an ECONOMICAL one?Relaxing the PT a bit for stacked parts is pretty easy.

Also they did build PVC and are doing CWF et al so they're familiar with thermals in 3D at least.

LightningZ71

Platinum Member

It was potentially the best consumer AVX 512 offering up to that point and until Zen4 was about the best you'd get. Tiger Lake H was decent per clock, but didn't get up there very well. I always wondered what they could have squeezed out of an honest attempt at making 12 P Bartlett Lake a high performance part.Yes, and I had one. I think it was a 12700k, but correct me if I am wrong on the model number. and I did disable the little cores and ran a avx-512 app and it started taking 300 watts ! (per my kill-a-watt)

Markfw

Moderator Emeritus, Elite Member

well, I think that power usage is out of the park. I sold it right after that. I got a Zen 3, and then when Zen 4 came out, it could do avx-512 using WAY less power. My 64 core Zen 4 just hits that on 64 cores, not 8.It was potentially the best consumer AVX 512 offering up to that point and until Zen4 was about the best you'd get. Tiger Lake H was decent per clock, but didn't get up there very well. I always wondered what they could have squeezed out of an honest attempt at making 12 P Bartlett Lake a high performance part.

Last edited:

LightningZ71

Platinum Member

Our amplifiers go up to 11, see? We were the loudest because of that!

adroc_thurston

Diamond Member

Oh no my friend, GPUs have nightmarish hotspots too.The difference being that server applications run at significantly lower frequencies with far more manageable hot spots as a result.

See AMD heatmap for MI300 (it's from HC'23 or '24 I forgot which one).

LightningZ71

Platinum Member

I thought CWF is a server CPU package? I didn't think PVC ever really went anywhere but a handful of HPC projects outside of the very late Aurora.

adroc_thurston

Diamond Member

Me point is they have more than enough experience modeling nightmarish hotspots too.I thought CWF is a server CPU package? I didn't think PVC ever really went anywhere but a handful of HPC projects outside of the very late Aurora.

Makaveli

Diamond Member

It's never been available at launch why would that change now?If they don't have X3D "available" at launch it'll be disappointing

gdansk

Diamond Member

NecessityIt's never been available at launch why would that change now?

Win2012R2

Golden Member

9800X3D is a top seller and prime target for upgrades, but nobody of them will buy anything other than Zen 6 X3D, earlier release can also add extra premiumIt's never been available at launch why would that change now?

However given very high demand for server chips consumer Zen6 might just get delayed or they will have very limited quantities that will sell anyway.

TRENDING THREADS

-

Discussion Zen 5 Speculation (EPYC Turin and Strix Point/Granite Ridge - Ryzen 9000)

- Started by DisEnchantment

- Replies: 25K

-

Discussion Intel Meteor, Arrow, Lunar & Panther Lakes + WCL Discussion Threads

- Started by Tigerick

- Replies: 25K

-

Discussion Intel current and future Lakes & Rapids thread

- Started by TheF34RChannel

- Replies: 24K

-

-